PMC-UART-28

PMC Compatible UART Interface

| Custom programmed interfaces are available. Please send us a timing diagram, and we can program one for you. Most interfaces can be adapted from our large library of designs within 2-3 weeks including the updated VHDL, Windows or Linux or VxWorks Driver, reference manuals etc. We can support on-site [ours] integration to help you get your application level software working. Alternatively choose one of the already completed versions and purchase off-the-shelf. Common requested and implemented interface types include: Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. Mix and Match. Just like but different... |

|

| |

|

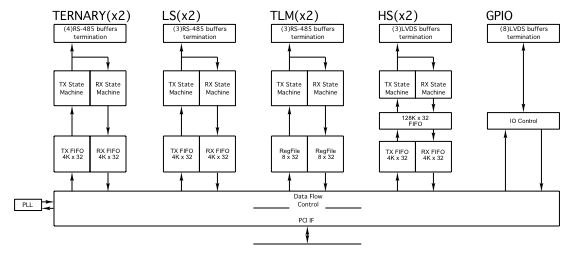

| 34 RS-485 / RS-422 / LVDS compatible IO are provided. Any combination of transmit or receive channels can be created. LVDS and RS-485 can be mixed. RS-485 bandwidth is lower when mixed [16 Mbps]. Programmable termination. Pull-up and Pull-down option on IO to allow controlled level when tri-stated. Option for marking or low state. |

|

| |

|

| The IO is available via the PMC bezel connector and / or the PMC "user IO" connector Pn4. The differential IO is properly routed with impedance control, pitch, and space plus matched lengths across all of the pairs. 0 ohm resistors are used to isolate the front and rear panel IO to allow single port designs to remove the bus stub to the removed port. Please note that the lower 32 channels [only] are routed to Pn4 due to pin limitations. |

|

| Up to 40 MHz RS485, and up to 200 MHz LVDS signaling supported. 4 channel software programmable PLL. Reference oscillator. Counters / Dividers / DCM for local clock control. |

|

| |

|

| PCI 33 MHz. operation Standard Target accesses, and "Channelized DMA"™ supported. "Channelized DMA"™ is a full DMA capability on each function in a multi-function implementation. Standard 32 bit operation supported. |

|

| PMC registers are read-writeable. VxWorks, Linux and Windows® drivers available. Design help for alternate OS implementations. | |

| An 8 bit "DIP Switch" is provided for user purposes. The DIP switch can be used to allow the application software to positively identify a PMC BiSerial VI in a multi-board implementation. The PCI bus enumerates the address which means the application software can´t rely on the address to always match up with a particular card. With the DIP switch the particular BiSerial can be identified and postive control over a particular asset provided. Could be important depending on what you are connected to. The switch can also be used for software control, a debugging aide or other user purposes. | |

| Software programmable interrupts on status, errors, completion of transfer, DMA, FIFO levels, custom events. Status can be polled for non-interrupt driven operation as well. |

|

| Separate FIFO´s / Dual Port RAM are provided for all channels. Internal FPGA Block RAM memory modules for fast access. Optional discrete FIFO´s -128K x 32 are available. |

|

| Xilinx Spartan VI 100 3I is the base FPGA installed. FLASH is used to program the FPGA. In many cases any feature updates can be sent to your facility to reprogram without down time. | |

| |

|

| +5, 3.3V. 2.5V and 1.2V converted with on-board power supply. |

|

| Industrial Temperature is standard. [-40 <=> +85]. | |

| Standard [leaded] processing or ROHS compliant processing are available. See ordering options. | |

| Conformal Coating is available to support operation in condensing environments. | |

| |

|

| Standard Single PMC |

|

| |

|

| Download PDF here |

| PMC-BiSerial-VI is optimized for differential interfacing requirements. The FIFO memories and programmable interrupts off-load the CPU from most of the management other implementations require. FIFO access is optimized for the PCI bus further reducing overhead by speeding up the data transfer. On the IO side the PMC BiSerial has independent channel functions. Channels can operate at maximum rate in parallel. With the Spartan VI "Channelized DMA"™ can be implemented and still have plenty of gates left for your application. |

|

| |

|

| PMC BiSerial is easily programmed to implement new functions. Many previously implemented "custom designs" are available too. Without the costs of schematic level design, layout, debugging etc. a modified PMC-BiSerial-VI will represent a large cost savings in your budget. With our large and growing VHDL library your function(s) may be close to complete when we start since we can modify existing implementations or repackage them as required. |

|

| |

|

| PMC-BiSerial-VI is easy to use. The registers are designed to be R/W without layering or other indirect control methods. Use the Dynamic Driver with Windows® VxWorks, or Linux or create your own. The HW manuals have the full address and bit maps plus definitions for each function. In most cases the interfaces are "Point and shoot" - just fill the FIFO and set the start bit to get your custom protocol transmitting. The driver and user application reference software have built in utilities for parsing new PLL frequency files, loading the PLL, reading the switch, doing loop-back using DMA via the IO and between FIFO´s. Built in loop-back capabilities and engineering kits help with integration into your system. We can write a custom for you. |

|

| |

|

| Dynamic Engineering plans to keep the PMC BiSerial VI in stock. Send in your order and in most cases have your hardware the next day. With a custom design a 2-3 week design period is usually required. We can support immediately with the another version then send updated FLASH Files later to help get your project going - right away. |

|

| |

|

| PMC BiSerial VI is a standard single wide PMC card and meets the PMC mechanical specifications. The PMC BiSerial VI can be used in all PMC slots. |

|

| |

|

| PMC BiSerial is PMC compliant per the IEEE 1386 specification. | |

| |

|

| PMC BiSerial is PCI compliant. You can develop with a PCI/PCIe etc. to PMC adapter - PCI2PMC or PCIePMCX1. Use the Java pull-down menu´s for more carrier options. |