## **DYNAMIC ENGINEERING**

150 DuBois St., Suite C Santa Cruz, CA 95060 (831) 457-8891 **Fax** (831) 457-4793 <u>http://www.dyneng.com</u> sales@dyneng.com Est. 1988

# **User Manual**

# PCI-NECL2-RTN10

# Bidirectional NECL I/O with DMA 12 bit GPIO port [TTL]

Revision A3 Corresponding Hardware: Revision B 10-2011-0102 Corresponding Firmware: Revision A 12/18/17

Embedded Solutions

## PCI-NECL2-RTN10

PCI format Full Duplex Byte Wide Port NECL port Supported with large SDRAM based FIFO GPIO - TTL Port

#### **Dynamic Engineering**

150 DuBois St., Suite C Santa Cruz, CA 95060 (831) 457-8891 FAX: (831) 457-4793

This document contains information of proprietary interest to Dynamic Engineering. It has been supplied in confidence and the recipient, by accepting this material, agrees that the subject matter will not be copied or reproduced, in whole or in part, nor its contents revealed in any manner or to any person except to meet the purpose for which it was delivered.

Dynamic Engineering has made every effort to ensure that this manual is accurate and complete. Still, the company reserves the right to make improvements or changes in the product described in this document at any time and without notice. Furthermore, Dynamic Engineering assumes no liability arising out of the application or use of the device described herein.

The electronic equipment described herein generates, uses, and can radiate radio frequency energy. Operation of this equipment in a residential area is likely to cause radio interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Dynamic Engineering's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Dynamic Engineering.

Connection of incompatible hardware is likely to cause serious damage.

Embedded Solutions

# Table of Contents

| PRODUCT DESCRIPTION PART I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| PRODUCT DESCRIPTION PART II                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 11                                                                                                                                                  |

| PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                                                                                                                                  |

| ADDRESS MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16                                                                                                                                                  |

| PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 17                                                                                                                                                  |

| REGISTER DEFINITIONS - BASE<br>RTN10_BASE_PLL<br>RTN10_BASE_SWITCH<br>RTN10_BASE_STATUS<br>RTN10_BASE_GPIO_DIR<br>RTN10_BASE_GPIO_DATA<br>RTN10_BASE_GPIO_IO                                                                                                                                                                                                                                                                                                                                                                                                             | <b>19</b><br>19<br>21<br>22<br>23<br>24<br>24                                                                                                       |

| REGISTER DEFINITIONS – CHANNEL<br>RTN10_CHAN_CNTRL<br>RTN10_CHAN_STATUS<br>RTN10_CHAN_WR_DMA_PNTR<br>RTN10_CHAN_TX_FIFO_COUNT<br>RTN10_CHAN_RX_FIFO_COUNT<br>RTN10_CHAN_FIFO<br>RTN10_CHAN_FIFO<br>RTN10_CHAN_TX_AMT_LVL<br>RTN10_CHAN_TX_AMT_LVL<br>RTN10_CHAN_TX<br>RTN10_CHAN_TX<br>RTN10_CHAN_TX_READY_REG<br>RTN10_CHAN_RX_MEM_A<br>RTN10_CHAN_RX_MEM_A<br>RTN10_CHAN_SET_MEM<br>RTN10_CHAN_SET_MEM<br>RTN10_CHAN_SET_MEM<br>RTN10_CHAN_TX_MEM_B<br>RTN10_CHAN_TX_MEM_B<br>RTN10_CHAN_TX_MEM_C<br>RTN10_CHAN_TX_MEM_C<br>RTN10_CHAN_TX_MEM_D<br>RTN10_CHAN_TX_MEM_D | <b>25</b><br>28<br>32<br>33<br>34<br>35<br>36<br>36<br>36<br>36<br>36<br>37<br>38<br>39<br>41<br>41<br>41<br>42<br>42<br>42<br>42<br>43<br>43<br>44 |

| RTN10_CHAN_RX_LOOP_CNT<br>RTN10_CHAN_TX_LOOP_CNT<br>RTN10_CHAN_RX_SDRAM_CMD<br>RTN10_CHAN_TX_SDRAM_CMD<br>RTN10_CHAN_TX_REF_COUNT | 45<br>45<br>46<br>46<br>47 |

|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| LOOP-BACK                                                                                                                         | 48                         |

| D100 STANDARD PIN ASSIGNMENT                                                                                                      | 49                         |

| APPLICATIONS GUIDE                                                                                                                | 51                         |

| Interfacing                                                                                                                       | 51                         |

| Construction and Reliability                                                                                                      | 52                         |

| Thermal Considerations                                                                                                            | 52                         |

| WARRANTY AND REPAIR                                                                                                               | 53                         |

| Service Policy<br>Out of Warranty Repairs                                                                                         | <b>53</b><br>53            |

| For Service Contact:                                                                                                              | 53                         |

| SPECIFICATIONS                                                                                                                    | 54                         |

| ORDER INFORMATION                                                                                                                 | 56                         |

# List of Figures

| FIGURE 1  | PCI-NECL2-RTN10 PLL                               | 7  |

|-----------|---------------------------------------------------|----|

| FIGURE 2  | PCI-NECL2-RTN10 BLOCK DIAGRAM                     | 8  |

| FIGURE 3  | PCI-NECL2-RTN10 INPUT TERMINATION                 | 9  |

| FIGURE 4  | PCI-NECL2-RTN10 OUTPUT TERMINATION                | 9  |

| FIGURE 5  | PCI-NECL2-RTN10 XILINX BASE ADDRESS MAP           | 16 |

| FIGURE 6  | PCI-NECL2-RTN10 XILINX CHANNEL ADDRESS MAP        | 16 |

| FIGURE 7  | PCI-NECL2-RTN10 BASE CONTROL REGISTER             | 19 |

| FIGURE 8  | PCI-NECL2-RTN10 ID AND SWITCH BIT MAP             | 21 |

| FIGURE 9  | PCI-NECL2-RTN10 STATUS PORT BIT MAP               | 22 |

| FIGURE 10 | PCI-NECL2-RTN10 GPIO DIRECTION BIT MAP            | 23 |

| FIGURE 11 | PCI-NECL2-RTN10 GPIO OUTPUT DATA BIT MAP          | 24 |

| FIGURE 12 | PCI-NECL2-RTN10 GPIO INPUT DATA BIT MAP           | 24 |

| FIGURE 13 | PCI-NECL2-RTN10 CHANNEL CONTROL REGISTER          | 25 |

| FIGURE 14 | PCI-NECL2-RTN10 CHANNEL STATUS PORT               | 28 |

| FIGURE 15 | PCI-NECL2-RTN10 WRITE DMA POINTER REGISTER        | 32 |

| FIGURE 16 | PCI-NECL2-RTN10 TX FIFO DATA COUNT PORT           | 33 |

| FIGURE 17 | PCI-NECL2-RTN10 READ DMA POINTER REGISTER         | 34 |

| FIGURE 18 | PCI-NECL2-RTN10 TX FIFO DATA COUNT PORT           | 35 |

| FIGURE 19 | PCI-NECL2-RTN10 RX/TX FIFO PORT                   | 36 |

| FIGURE 20 | PCI-NECL2-RTN10 TX ALMOST EMPTY LEVEL REGISTER    | 36 |

| FIGURE 21 | PCI-NECL2-RTN10 RX ALMOST FULL LEVEL REGISTER     | 36 |

| FIGURE 22 | PCI-NECL2-RTN10 CHANNEL TRANSMIT CONTROL REGISTER | 37 |

| FIGURE 23 | PCI-NECL2-RTN10 TX HOLD OFF REGISTER              | 38 |

| FIGURE 24 | PCI-NECL2-RTN10 CHANNEL RX CONTROL REGISTER       | 39 |

| FIGURE 25 | PCI-NECL2-RTN10 RX MEMORY A REGISTER              | 41 |

| FIGURE 26 | PCI-NECL2-RTN10 TX MEMORY A REGISTER              | 41 |

| FIGURE 27 | PCI-NECL2-RTN10 SET MEMORY REGISTER               | 42 |

| FIGURE 28 | PCI-NECL2-RTN10 RX MEMORY B REGISTER              | 42 |

| FIGURE 29 | PCI-NECL2-RTN10 TX MEMORY B REGISTER              | 42 |

| FIGURE 30 | PCI-NECL2-RTN10 RX MEMORY C REGISTER              | 43 |

| FIGURE 31 | PCI-NECL2-RTN10 TX MEMORY C REGISTER              | 43 |

| FIGURE 32 | PCI-NECL2-RTN10 RX MEMORY D REGISTER              | 44 |

| FIGURE 33 | PCI-NECL2-RTN10 TX MEMORY D REGISTER              | 44 |

| FIGURE 34 | PCI-NECL2-RTN10 RX LOOP COUNT REGISTER            | 45 |

| FIGURE 35 | PCI-NECL2-RTN10 TX LOOP COUNT REGISTER            | 45 |

| FIGURE 36 | PCI-NECL2-RTN10 RX SDRAM COMMAND REGISTER         | 46 |

| FIGURE 37 | PCI-NECL2-RTN10 TX SDRAM COMMAND REGISTER         | 46 |

| FIGURE 38 | PCI-NECL2-RTN10 TX REFERENCE COUNT PORT           | 47 |

| FIGURE 39 | PCI-NECL2-RTN10 STANDARD D100 PINOUT              | 49 |

Embedded Solutions

# **Product Description Part I**

Naming: PCI-ECL-II is the base design and can be outfit with NECL and other ECL family components. The specific versions of the implementation will have the "ECL" changed to "NECL" etc. plus an extension added for the VHDL set and any other alterations made to the board.

RTN10 uses the classic negative ECL or NECL plus a specific FPGA file set designed to provide byte wide data transfers at a programmable IO rate. A receiver is also designed in which can operate in parallel with the transmitter. One of the two available channels is tied to the IO [channel 0]. The second channel has memory and loop-back capabilities but no IO in this implementation. RTN10 is an upgrade from the original STE3A design. Enough changes are incorporated that we changed the name and CardId to properly identify the design. RTN10 is recommende for new designs.

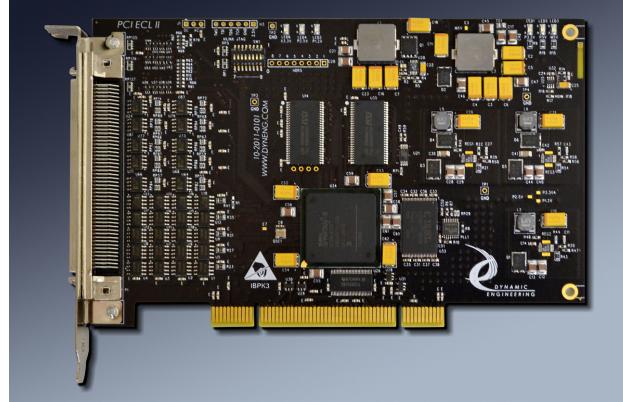

PCI-NECL2-RTN10 is part of the PCI Compatible family of modular I/O components. PCI-NECL2-RTN10 provides a Spartan 6 FPGA, along with 40 ECL [NECL] and 12 TTL I/O lines, a programmable PLL and FIFO support with full bidirectional DMA capabilities in a half-length single slot card.

The FIFO's are based on SDRAM devices with programmable offsets to allow the memory to be partitioned into 1 or 2 sections per port. The sections can be the same size or programmed for different RX and TX sizes. The total memory per port is 32 Mbytes.

The RTN10 version of the design adds clocking and framing options. Select rising or falling edge stable output on transmit and rising or falling edge capture for Rx. Also select the option to not use the enable and capture all data presented at the Rx port.

The PCI bus implementation is 32 bits at 33 MHz, universal voltage. The hardware supports direct access software controlled read/write access to all locations plus DMA support to the high bandwidth FIFO ports. The hardware is optimized for simultaneous bidirectional DMA access to support the high data rates available on the PCI-NECL2-RTN10.

The Cypress 22393 PLL is handy for creating user specific frequencies with which to operate the state-machines and I/O. The driver supports programming the PLL over a serial I<sup>2</sup>C bus. Four clocks are received from the PLL into the FPGA - see figure 1 below. The clock routing uses matched lengths to provide in-phase references should they be necessary in your design. The FPGA clock features provide further clock functionality. RTN10 uses the on-board oscillator (50 MHz) as the reference for the

PLL, and PLLA is used to set the transmit frequency when used for loop-back. A .jed file can be used to set this frequency.

Cypress has a utility available for calculating the frequency control words for the PLL. http://www.dyneng.com/CyberClocks.zip is the URL for the Cypress software used to calculate the PLL programming words. The PLL responds to one of two device ids (only one works). As part of our ATP our software determines the address of the PLL. The software is part of the engineering kit and can be ported to your application.

FIGURE 1

PCI-NECL2-RTN10 PLL

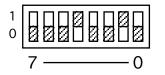

An 8-bit "dip switch" is provided on the PCI-NECL2-RTN10 for user-defined purposes. The switch configuration is readable via a memory-mapped I/O port. We envision the switch being used for software configuration control, PCI board identification or test purposes.

LED's are provided on the board to indicate that the 3.3, 2.5, 1.2, and -5V regulators are operating properly plus the PCI 5V and 3.3V. Local regulation is provided for 3.3, 2.5, 1.2, and -5V volts. The 3.3V regulator is used for the Spartan 6 due to a lower Vmax than the PCI supplied 3.3V. Each of the voltages other than the PCI 3.3V and 5V have voltage comparators controlling the LED's. For example, when the –5V LED is illuminated if it is within tolerance.

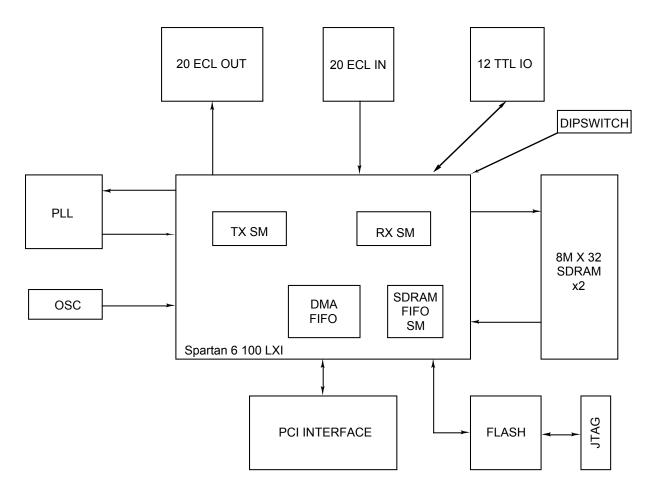

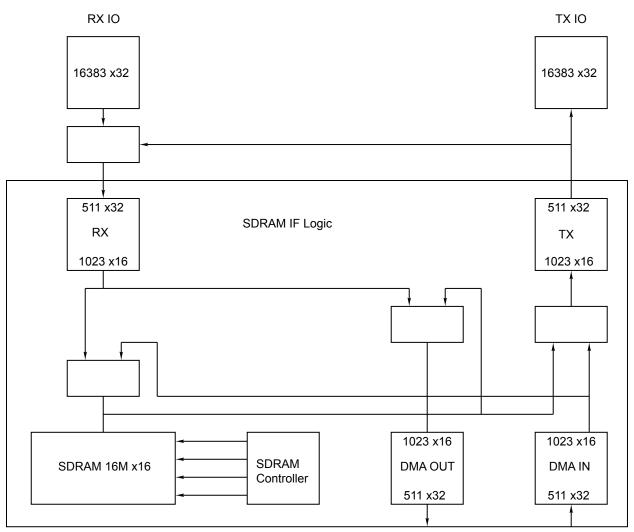

#### FIGURE 2

PCI-NECL2-RTN10 BLOCK DIAGRAM

PCI-NECL2-RTN10 has both NECL and TTL I/O interfaced to the D100 connector. There are 20 NECL inputs and 20 NECL outputs on the board as indicated in figure 2 above. RTN10 uses the first 10 IO for transmit and receive plus number 18 for a reference clock. 7-0 = data, 8 = enable, 9 = clock.

12 TTL I/O lines are supported with open drain drivers with pull-ups. The LVC1G125 open drain drivers have 64+ mA of sink capability. The IO can be referenced to 3.3 or 5V. Please note the '125's are 3.3V devices and when enabled and driven "hi" the output will be pulled down to 3.3V. To achieve 5V on the IO, the driver is disabled allowing the resistor to pull to the 5V level. The reference can also be set to 3.3V in which case the driven [hi] and off states are the same. Each IO can be set to drive or be an input independently. RTN10 has a GPIO port for this purpose.

```

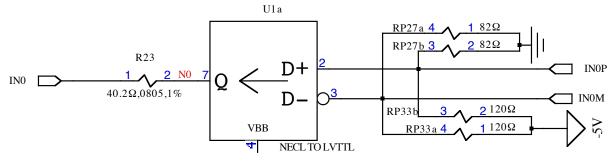

FIGURE 3

```

The NECL inputs are terminated with 50 $\Omega$  to -2V using a parallel 82 $\Omega$  / 120 $\Omega$  equivalent circuit as shown in figure 3 above. The NECL input lines are routed as differential pairs with matched lengths and impedance control [trace and space]. The lengths are matched from the connector edge to the Xilinx ball to allow for high-speed low-skew operation.

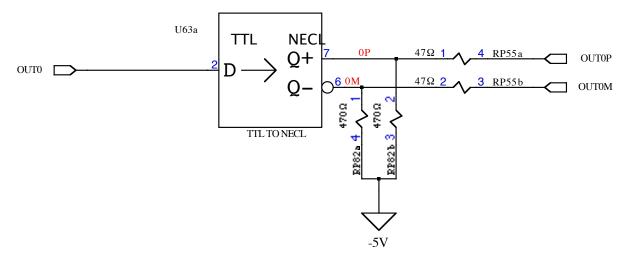

#### FIGURE 4

PCI-NECL2-RTN10 OUTPUT TERMINATION

The NECL outputs are terminated with  $470\Omega$  terminations to -5V. The NECL output lines are routed as differential pairs with matched lengths and impedance control [trace and space]. The lengths are matched from the Xilinx ball to the connector edge to allow for high-speed low-skew operation.

The Xilinx FPGA is re-configurable by loading a new programming file into the FLASH storage device. The file can be generated with the standard Xilinx design software. The standard Xilinx Parallel JTAG cable is connected to the on-board header to program the FLASH using the Xilinx iMPACT software.

PCI-NECL2-RTN10 INPUT TERMINATION

The engineering kit includes a cable and the HDEterm100. The HDEterm100 serves as a breakout from the cable to screw terminal block. HDEterm100 has matched length, differential routing and several termination options that can be installed. For more information on the HDEterm100 please visit the web page. http://www.dyneng.com/HDEterm100.html

In addition a "cross over" cable is available which interconnects the ECL IN and OUT IO are cross connected 1:1 to allow two boards to connected for data transfer. The TTL lines are connected 1:1 between the boards. This cable is used for our two board testing.

The PLL is used to set the TX rate indirectly. RTN10 uses the clock received on NECL Input 18 as the transmit rate reference. PLLA is used to generate NECL Output 18. With the cross over cable Card 1 PLLA will be used as the reference for Card 2 and vice-versa. Output 18 can be looped back to Input 18 to use the PLL as the local reference. [This is done in the user cable.]

RTN10 is tested at 29.4 MHz with the .jed file included with the reference SW. New .JED files can be produced with the Cypress Semiconductor CyberClocks application. The local oscillator frequency is 50 MHz.

# **Product Description Part II**

A wide range of interfaces and protocols can be implemented with the PCI-ECL-II; UART, Manchester encoding, serial or parallel, ECL/NECL and/or TTL. The interfaces can be created using the hardware and development tools provided with the PCI-ECL along with the Xilinx software.

Once your requirements are known the design can be implemented with VHDL and compiled with the Xilinx design software. The output file can be programmed into the Xilinx Flash. Because the FLASH is reprogrammable, the design can be implemented in phases. Experiment and test out concepts and partial implementations during the design phase or perhaps simulate other hardware that needs to be implemented.

As an example consider a parallel interface with 16 data lines and 3 control signals. The PCI-ECL-II has 40 ECL differential I/O, so there is enough I/O for a full duplex implementation. The parallel channel would be supported with the 8Mx32 [SDRAM] FIFO plus any internal FIFO's that were instantiated out of block RAM. The FPGA is a Spartan 6 LX100 industrial temp part in the –3 speed grade. The PCI interface and SDRAM controller only occupy a small percentage of the device. RTN10 including everything uses approximately 19%. There is of room for more complex data formatting requirements.

For systems with an external reference clock, ECL input bits 19, 18, 17, 16 and 9 are received by the FPGA on a long line pins. They can be routed through a Digital Clock Manager to create a low skew clock distribution based on an external reference.

The data flow for transmission is Host memory transferred into the transmit FIFO via DMA transfers. The user state machine reads the data from the FIFO on the output side and applies the user protocol before transmitting. On the receive side the data flows into the FPGA, is processed to convert to a format suitable for storing, and then loaded into the receive FIFO. The data is read from the receive FIFO by the PCI control state-machine and moved into the host memory via DMA transfers.

The path to the Transmit or from the Receive local FIFO's is indirect. In the Tx path the PCI DMA transfers to the SDRAM TX DMA FIFO within the SDRAM group. The FIFO is read by the SDRAM controller and the data moved to the SDRAM. The data stored in the SDRAM is moved to the output FIFO within the SDRAM group. The SDRAM controller uses the state of the FIFO's and SDRAM to determine when to move data or not. The Tx state-machine reads from the Tx IO FIFO in the SDRAM group to interface with the Tx encoding for that design. In RTN10 a secondary TX FIFO [16Kx32] is used to convert between the 33 MHz and the user TX rate. Separate logic converts from 32 bits to the 8 bits transmitted.

The receive path is similar with the receiver controller using a rate matching local FIFO and moving data to the SDRAM RX IO FIFO. The RX IO FIFO is read by the SDRAM controller and moved to the SDRAM. From the SDRAM, data is loaded to the SDRAM RX DMA FIFO for transfer to the host memory.

The SDRAM controller block has FIFO counts available to allow the TX and RX SM to properly interact with the FIFO's built into the SDRAM controller.

The SDRAM controller automatically uses page mode and single transfers based on data and space available. RTN10 operates at 132 MHz within the SDRAM controller, internal FIFO ports and SDRAM.

The SDRAM controller has bypass transfer units which if enabled move data directly from the SDRAM TX DMA FIFO to the SDRAM TX IO FIFO and similarly from the SDRAM RX IO to the SDRAM RX DMA FIFO's. Each bypass is independent. This allows all of the SDRAM to be tied to one port or the other.

The SDRAM controller has an arbitration unit which determines on a round-robin basis which channel to service next. When an operation completes the arbiter looks at each of the other options before checking the same channel again. The logic has skip-ahead to save states when a channel is disabled.

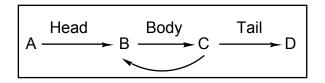

The TX and RX have load and unload operations with separate enables to allow the software to configure TX only, RX only, TX load before start-up etc. The design includes a FIFO mode and a retransmit mode. The retransmit mode has the ability to send a header, body, and tail. The FIFO mode makes the SDRAM act like a FIFO and is the mode used in the RTN10. Please see the programming section for more details.

The full bandwidth of the PCI bus is utilized during DMA transfers. There is some overhead on the PCI bus side, which will limit the actual sustainable transfer rate somewhat compared to the theoretical limit. Looking at the other side of the equation; if we assume parallel data with 1 channel operating at 35 Mbytes/second in each direction, this creates a total of 70 Mbytes/second on the PCI bus – approximately 53% loading of the theoretical maximum.

Using the same example and looking at the storage, one can see that the OS can "go away" for 4M words x 4 bytes/word / 70Mbytes/sec => 239.6 mS without receive data over-running the FIFO when used for receive or under-running the FIFO when used for transmit. With Windows® and other high level OS based system the OS can neglect data movement due to other requirements - dealing with the keyboard or HDD for example. Having adequate storage can make a big difference in system performance.

The memory diagram shows the paths and sizes of the available memory for one port. There are two ports in RTN10. All of the IO is attached to port 0. Port 1 does have the memory shown. As described above the memory has a lot of options for controlling data path. Include SDRAM or bypass, perform loop-back at various locations or not, asymmetric or symmetric operation with Rx and Tx. Programmable sizes for the Rx and Tx memory allowing more SDRAM to be allocated to your programs requirements. Please refer to the register definitions for the details of programming the SDRAM.

### **Current Feature List**

- Xilinx Spartan 6 series FPGA

- Bidirectional DMA capable 32/33 PCI bus interface

- PLL with 4 programmable clocks tied to FPGA

- 8M x 32 Data buffer per port [RX/TX pair]

- 20 ECL Outputs

- 20 ECL Inputs

- 12 TTL I/O

- 8 position "DIP Switch"

- Power LED's

- On-going development with a "FLASH" program

As Dynamic Engineering adds features to the hardware we will update the PCI-ECL-II page on the Dynamic Engineering website. If you want some of the new features, and have already purchased hardware, we will support you with a FLASH update. We will reprogram the FLASH on your board for you or if you have the engineering kit and your own download cable, send you the new bit file. If you are interested please contact sales@dyneng.com for arrangements.

The basic PCI identifying information will not change with the updates. The revision field will change to allow configuration control. STE3 is design 1 STE3A is design 2, RTN10 is design 3 for the PCI-ECL-II. See the Switch and Status section for FLASH revision information.

Revision 3 is the current fab for PCI-ECL-II. 10-2011-0103 is the complete fab number.

# Programming

PCI-NECL2-RTN10 is tested in a Windows and Linux environment. We use our driver to support our test software. Please consider purchasing the engineering kit for the PCI-NECL2-RTN10; the kit comes with a cable and breakout. The Linux and Win7 drivers are included with the purchase of the board. Please specify which driver you prefer.

The internal registers for the Xilinx are defined in the following pages.

The architecture is designed as a hierarchy with a Base and Channels. There are two ports/channels implemented for RTN10. Port 0 has is tied to the NECL IO and is the "active" port. port 1 has a separate memory and can be accessed. No IO is connected to port 1 at this time.

The address maps are offsets from the base address. In the case of the Base the offset is the system assigned memory space address. The channels are shown relative to 0x00 for the channel. The channels are offset from the base and each other as shown.

Feature Address offset Decodes

Base 0x00 19-0 Channel 0 0x50 39-0 (59-20) Channel 1 0xF0 39-0 (99-60)

The VendorID is 0xDCBA The CardID for RTN10 is 0x0062

The address map provided is for the local decoding performed within PCI-NECL2-RTN10. The addresses are all offsets from a base address. The base address and interrupt level are provided by the host.

The host system will search the PCI bus to find the assets installed during power-on initialization and allocate memory and interrupt resources.

Once the initialization process has occurred and the system has assigned an address range to PCI-NECL2-RTN10, the software will need to determine what the address space is. We refer to this address as base0 in our software.

The next step is to initialize the PCI-NECL2-RTN10. The local Xilinx registers need to be configured. Please refer to the included SW for the initialization sequences.

## **Address Map**

#### Base Addresses

RTN10 BASE PLL 0x00000000 // 0 Base control register 0x00000004 // 1 Switch, Xilinx Revision, Design RTN10 BASE SWITCH Number RTN10 BASE STATUS 0x0000008 // 2 Base Status RTN10\_BASE\_GPIO\_DIR0x00000010 // 4 GPIO Direction registerRTN10\_BASE\_GPIO\_DATA0x00000014 // 5 GPIO Data registerRTN10\_BASE\_GPIO\_IO0x00000018 // 6 GPIO Data in: read only

#### **FIGURE 5**

#### PCI-NECL2-RTN10 XILINX BASE ADDRESS MAP

0x00000000 // 0 General Control Register

#### Channel Addresses

RTN10 CHAN CNTRL RTN10\_CHAN\_STATUS0x00000004 // 1 Interrupt Status Port Read OnlyRTN10\_CHAN\_INT\_CLEAR0x00000004 // 1 Interrupt Clear Port Write Only RTN10 CHAN WR DMA PNTR 0x0000008 // 2 TX Wr DMA Port physical PCI address register address reg RTN10 CHAN FIFO FIFO RTN10 CHAN TX before TX

RTN10\_CHAN\_RX\_MEM\_A RTN10\_CHAN\_TX\_MEM\_A RTN10\_CHAN\_SET\_MEM set RTN10\_CHAN\_RX\_MEM\_D0x000006C // 27 Receive address DRTN10\_CHAN\_TX\_MEM\_D0x00000070 // 28 Transmit address D

RTN10 CHAN RX

RTN10\_CHAN\_TX\_FIF0\_COUNT 0x0000008 // 2 TX FIF0 data count - read only RTN10 CHAN RD DMA PNTR 0x000000C// 3 RX Read DMA Port Physical PCI RTN10 CHAN RX FIFO CNT 0x0000000C // 3 RX FIFO data count - read 0x00000010 // 4 Single Word Access port for TX, RX RTN10\_CHAN\_TX\_AMT\_LVL0x00000014 // 5 TX almost empty level register R/WRTN10\_CHAN\_RX\_AFL\_LVL0x00000018 // 6 RX Almost Full level register R/W 0x00000014 // 5 TX almost empty level register R/W 0x0000001C // 7 TX Control Register R/W RTN10 CHAN TX READY REG 0x0000002C // 11 Num of bytes req. in final FIFO 0x0000034 // 13 RX Control Register R/W 0x00000050 // 20 Receive address A 0x00000054 // 21 Transmit address A 0x00000058 // 22 Spare - reserved for direct memory RTN10\_CHAN\_RX\_MEM\_B0x0000005C // 23 Receive address BRTN10\_CHAN\_TX\_MEM\_B0x00000060 // 24 Transmit address BRTN10\_CHAN\_RX\_MEM\_C0x00000064 // 25 Receive address CRTN10\_CHAN\_TX\_MEM\_C0x00000068 // 26 Transmit address C 0x000005C// 23 Receive address B

RTN10 CHAN RX LOOP CNT 0x00000074 // 29 Receive Body Loop Count 7-0 RTN10 CHAN TX LOOP CNT 0x00000078 // 30 Transmit Body Loop Count 7-0 RTN10 CHAN RX SDRAM CMD 0x000007C // 31 Receive SDRAM Control Register 7-0 RTN10 CHAN TX SDRAM CMD 0x0000080 // 32 Transmit SDRAM Control Register 7-0

#### FIGURE 6

#### PCI-NECL2-RTN10 XILINX CHANNEL ADDRESS MAP

Embedded Solutions

# Programming

Programming the PCI-NECL2-RTN10 requires only the ability to read and write data in the host's PCI space.

Once the initialization process has occurred, and the system has assigned addresses to the PCI-NECL2-RTN10 card the software will need to determine what the address space is for the PCI interface [BAR0]. The offsets in the address tables are relative to the system assigned BAR0 base address.

The next step is to initialize PCI-NECL2-RTN10. The PLL will need to be programmed to use the loop-back function. The Cypress CyberClocks software can be used to create new .JED files if desired. PLLA should be set to the transmit reference frequency output by the transmitter.

The driver comes with a .JED file prepared. The driver has a utility to load the PLL and read back. The reference application software has an example of the use of PLL programming. The reference application software also includes XLATE.c which converts the .JED file from the CyberClocks tool to an array that can be programmed into the PLL.

For Windows<sup>™</sup> and Linux systems the Dynamic Drivers can be used. The driver will take care of finding the hardware and provide an easy to use mechanism to program the hardware. The Driver comes with reference software showing how to use the card and reference frequency files to allow the user to duplicate the test set-up used in manufacturing at Dynamic Engineering. Using simple, known to work routines is a good way to get acquainted with new hardware.

To use the RTN10 specific functions the Channel Control, and PLL interface plus DMA will need to be programmed. To use DMA, memory space from the system should be allocated and the link list stored into memory. The location of the link list is written to RTN10 to start the DMA. Please refer to the Burst IN and Burst Out register discussions.

DMA should be set-up before starting the channel port function. For transmission this will result in the FIFO being full or close to it when the transfer is started or at least the Packet loaded if shorter than the FIFO size. To further facilitate continuous transmission the Ready Level is programmed to the number of LW desired to be in the Output FIFO before starting up. This allows the Transmitter to be enabled and start at the programmed level automatically.

For reception it means that the FIFO is under HW control and the delay from starting reception to starting DMA won't cause an overflow condition.

DMA can be programmed with a specific length. The length can be as long as you want within standard memory limitations. At the end of the DMA transfer the Host will receive an interrupt. With non-blocking DMA the application will be told how many bytes were transferred. With blocking the thread will wait for the programmed amount to be available in host memory before providing the interrupt. The receiver can be stopped and the FIFO reset to clear out any extra data captured.

For on-the-fly processing multiple shorter DMA segments can be programmed; at the interrupt restart DMA to point at the alternate segment to allow processing on the previous one. This technique is sometimes referred to as "ping-pong".

Please see the channel control register bit maps for more information.

# **Register Definitions - Base**

## RTN10\_BASE\_PLL

[0x0000 Main Control Register Port read/write]

DATA BIT DESCRIPTION

#### 31-21 spare

- 20 bit 19 read-back of pll\_dat register bit

- 19 pll\_dat [write to PLL, read-back from PLL]

- 18 pll\_s2

- 17 pll sclk

- 16 pll en

- 15 ResetInt

- 14-1 spare

- 0 BigEndianDma

FIGURE 7

PCI-NECL2-RTN10 BASE CONTROL REGISTER

This is the base control register for RTN10. The features common to all channels are controlled from this port. Unused bits are reserved for additional new features. Unused bits should be programmed '0' to allow for future commonality.

BigEndianDma : '0' disables this option. '1' enables this option. When operating with a Big Endian platform and using PCI accesses DMA can have challenges. The register accesses directly over the PCI bus are usually taken care of automatically with byte swapping within the CPU or PCI interface on the CPU. DMA data is written to or read from the local memory and is not swapped. The direct read/write from memory ends up with scrambled data [relative to little endian definitions]. Setting this bit will byte reverse the data for the DMA path into the Tx and out of the Rx FIFO's only. Register accesses are not affected.

31-24, 23-16, 15-8, 7-0  $\Leftrightarrow$  7-0, 15-8, 23-16, 31-24 byte swapping pattern implemented.

ResetInt is combined with the system reset to create an internal reset. Setting this bit '1' will cause a board level reset with all features except the PCI core, base control register, and certain clocking assets. Default and operational setting is '0'.

pll\_en: When this bit is set to a one, the signals used to program and read the PLL are enabled.

pll\_sclk/pll\_dat : These signals are used to program the PLL over the I<sup>2</sup>C serial interface. Sclk is always an output whereas Sdata is bi-directional. This register is

where the Sdata output value is specified or read-back.

pll\_s2: This is an additional control line to the PLL that can be used to select additional pre-programmed frequencies. Set to '0' for most applications.

The PLL is programmed with the output file generated by the Cypress programming tool. [CY3672 R3.01 Programming Kit or CyberClocks R3.20.00 Cypress may update the revision from time to time.] The .JED file is used by the Dynamic Driver to program the PLL. Programming the PLL is fairly involved and beyond the scope of this manual. For clients writing their own drivers it is suggested to get the Engineering Kit for this board including software, and to use the translation and programming files ported to your environment. This procedure will save you a lot of time. For those who want to do it themselves the Cypress PLL in use is the 22393. The output file from the Cypress tool can be passed directly to the Dynamic Driver [Linux or Windows] and used to program the PLL without user intervention. The reference frequency for the PLL is 50 MHz.

### RTN10\_BASE\_SWITCH

[\$04 Switch and Design number port read only] DATA BIT DESCRIPTION

31-24 Design Revision23-16 Design ID15-8 PCI Core Revision7-0 DIP switch

FIGURE 8

PCI-NECL2-RTN10 ID AND SWITCH BIT MAP

The DIP Switch is labeled for bit number and '1' '0' in the silk screen. The DIP Switch can be read from this port and used to determine which PCI-NECL2-RTN10 physical card matches each PCI address assigned in a system with multiple cards installed. The DIPswitch can also be used for other purposes – software revision etc. The switch shown would read back 0x12.

The Design ID and Revision are defined by a 16 bit field allowing for 256 designs and 256 revisions of each. The RTN10 design is 0x03 the current revision is 0x03.

The PCI revision is updated in HW to match the design revision. The board ID will be updated for major changes to allow drivers to differentiate between revisions and applications.

### RTN10\_BASE\_STATUS

[\$08 Board level Status Port read only] DATA BIT DESCRIPTION

31-21 set to '0

20 SDRAM Clock Locked

19-17 set to '0

- 16 PLLA Clock Locked

- 7-2 set to '0', reserved for additional channels

- 1 Unmasked Ch1 Interrupt

- 0 Unmasked Ch0 Interrupt

FIGURE 9

PCI-NECL2-RTN10 STATUS PORT BIT MAP

Channel Interrupt – The local interrupt status from the channel. Each channel can have different interrupt sources. DMA Write, DMA Read, IntForce or TX/RX request are typical sources. Polling can be accomplished using the channel status register and leaving the channel interrupt disabled.

The Clock Locked status when '1' indicate the corresponding DCM is in lock with the clock and can be used. SW should check this status before proceeding. The DCM's have logic to cause reacquisition of the clock should lock not be achieved. In most cases the status will be set immediately after reset for the SDRAM. The PLLA status will require the PLL to be programmed, a delay for the PLL to lock externally, and then for the local DCM to achieve lock. 10 mS for the PLL delay worst case after changing frequencies. An additonal 1 mS for the internal DCM.

Please note: the power up sequence should be to discover the card, initialize at the base level – program PLL, wait for lock in Base Status etc. Then check lock status in the channel and potentially check the frequency too. Once the channel is locked to the external clock proceed with initialization of the transmitter.

Embedded Solutions

## RTN10\_BASE\_GPIO\_DIR

[\$10 Board level GPIO Direction Register ] DATA BIT DESCRIPTION

| 31-16 | undefined                            |

|-------|--------------------------------------|

| 15-0  | '1' = TX, '0' = RX 11-0 tied to GPIO |

FIGURE 10

PCI-NECL2-RTN10 GPIO DIRECTION BIT MAP

The GPIO port consists of 12 TTL programmable IO. The IO control are register based and independent. Each IO can be enabled for transmit, or disabled for receive modes.

The IO can [as a bank] be tied to 3.3V or 5V. If set to 5V the IO will "float" at 5V unless the transmitter is enabled on the board or the "other end" is driving the cable. When the transmitter is enabled, the IO level will be near 3.3V or ground depending on the register IO bit definition. The 3.3V level comes from the 5V tolerant IO being driven with a 3.3V device. For seamless transitions the 3.3V reference is recommended [RTN10 selection] for true 5V operation the 5V high can be obtained with the output disabled, and the 0V level reached with the output enabled and defined as a low.

## RTN10\_BASE\_GPIO\_DATA

[\$14 Board level GPIO Data Register ] DATA BIT DESCRIPTION

31-16undefined15-0GPIO Output Data [11-0]

FIGURE 11

PCI-NECL2-RTN10 GPIO OUTPUT DATA BIT MAP

The GPIO port consists of 12 TTL programmable IO. The lower 12 bits correspond to the 12 port bits. When the transmitter is enabled with the corresponding Direction bit, the definition from this register will be driven onto the IO line.

Read-back provides the register contents – not necessarily the same as the IO definition as that can be affected by the external device.

### RTN10\_BASE\_GPIO\_IO

[\$18 Board level GPIO Input Register]

| DATA BIT | DESCRIPTION            |

|----------|------------------------|

| 31-16    | undefined              |

| 15-0     | GPIO Input Data [11-0] |

FIGURE 12

PCI-NECL2-RTN10 GPIO INPUT DATA BIT MAP

This port is read-only and returns the state of the TTL IO. If an external device is not connected the value will match the Output Data register if the direction bits are set. If an external device is connected the IO will match the IO and may not match the internal register definition.

# **Register Definitions – Channel**

The RTN10 design has 1 active channel and 1 passive channel. The basic control signals are the same for the channel base, channel status, FIFO and DMA interfaces across multiple designs.

#### Notes:

The offsets shown are relative to the channel base address not the card base address.

### RTN10\_CHAN\_CNTRL

[0x0] Channel Control Register (read/write)

#### **Channel Control Register**

| Data Bit | Description                |

|----------|----------------------------|

| 31-19    | spare                      |

| 18       | ByEnChRx                   |

| 17       | ByEnChTx                   |

| 16       | Init SDRAM                 |

| 15-10    | Spare                      |

| 9        | RstTxRefDcm                |

| 8        | OutUrgent                  |

| 7        | InUrgent                   |

| 6        | Read DMA Interrupt Enable  |

| 5        | Write DMA Interrupt Enable |

| 4        | Force Interrupt            |

| 3        | Channel Interrupt Enable   |

| 2        | Bypass                     |

| 1        | Receive FIFO Reset         |

| 0        | Transmit FIFO Reset        |

|          |                            |

FIGURE 13

PCI-NECL2-RTN10 CHANNEL CONTROL REGISTER

<u>FIFO Transmitter/Receiver Reset</u>: When set to a one, the transmit and/or receive FIFO's will be reset. When these bits are zero, normal FIFO operation is enabled. In addition the Transmit and Receive State Machines are also reset. The receive side is referenced to an internal 200 MHz clock. The transmit side is referenced to the received TX clock. The Transmit FIFO Reset must be applied once the TX reference clock is present.

RstTxRefDcm when set '1' will reset the DCM monitoring circuit which will in turn cause a requisition of the Tx Reference Clock. Occasionally when the frequency changes the DCM may not achieve lock. Hardware automatically will attempt to recycle through and obtain lock. This bit can be used to force the DCM to reacquire for the unlikely situation of the DCM staying in lock when the signal has changed. Use when the Tx Frequency determined from the Tx Reference Clock Count port does not match the expected frequency of update.

<u>Write/Read DMA Interrupt Enable</u>: These two bits, when set to one, enable the interrupts for DMA writes and reads respectively.

<u>Channel Interrupt Enable</u>: When this bit is set to a one, all enabled interrupts (except the DMA interrupts) will be gated through to the PCI interface level of the design; when this bit is a zero, the interrupts can be used for status without interrupting the host. The channel interrupt enable is for the channel level interrupt sources only.

<u>Force Interrupt</u>: When this bit is set to a one, a system interrupt will occur provided the Channel Interrupt enable is set. This is useful for interrupt testing.

<u>InUrgent / OutUrgent</u> when set causes the DMA request to have higher priority under certain circumstances. Basically when the TX FIFO is almost empty and InUrgent is set the TX DMA will have higher priority than it would otherwise get. Similarly if the RX FIFO is almost full and OutUrgent is set the read DMA will have higher priority. The purpose is to allow software some control over how DMA requests are processed and to allow for a higher rate channel to have a higher priority over other lower rate channels.

<u>ByPass</u> when set allows the FIFO to be used in a loop-back mode internal to the device. A separate state-machine is enabled when ByPass is set and the TX and RX are not enabled. The state-machine checks the TX and RX FIFO's and when not empty on the TX side and not Full on the RX side moves data between them. Writing to the TX FIFO allows reading back from the RX side. An example of this is included in the Driver reference software.

Init SDRAM when set causes the SDRAM controller to initialize the SDRAM. Initializing SDRAM is a specific sequence of steps the HW goes through to enable SDRAM operation. The bit is self clearing. Read-back can be used to determine if the initialization process has completed. The sequence is pretty rapid – the bit may be cleared by the time the SW returns to read it.

When Init SDRAM is set, the RTN10\_CHAN\_RX\_MEM\_A register is used to set the SDRAM parameters after which the register is returned to normal use. This register must be initialized with the SDRAM parameters prior to the "Init" bit being set.

Once running the init bit will not have effect on the SDRAM unless the SDRAM controller is reset – returned to the idle state. The FIFO resets can be used for this purpose.

Normally a once per power up cycle operation.

<u>ByEnChTx and ByEnChRx</u> when set enable the bypass data movers to operate for the Tx or Rx channels respectively.

The main memory is organized with 4 ports, the SDRAM "in the middle" and FIFO's on either side for RX or TX operation. SW causes data to move to the SDRAM DMA TX FIFO, data is automatically moved from the SDRAM DMA TX FIFO to the SDRAM or to the SDRAM IO TX FIFO directly. When the Bypass bit is set, the data is moved directly from FIFO to FIFO avoiding the SDRAM. This will improve latency [slightly] but remove the SDRAM memory from the path. The input and output FIFO's for the TX and RX direction are 512 x 32. Removing the SDRAM means a 1Kx32 FIFO between the PCI bus and the TX state machine or the RX state machine and the PCI bus.

The RX and TX state-machines have additional memory [16Kx32] for the RTN10 design.

When the bypass bits are disabled the data flows through the SDRAM allowing for a much larger storage space. The total memory is 8Mx32 and can be partitioned with SW. Please refer to the MEM registers for more information.

## RTN10\_CHAN\_STATUS

[0x4] Channel Status Read/Clear Latch Write Port

#### Channel Status Register

| Data Bit<br>31<br>30<br>29-25<br>24<br>23<br>22<br>21<br>20<br>19<br>18<br>17<br>16<br>15<br>14<br>13<br>12<br>11<br>10<br>9<br>8<br>7<br>6 | Description<br>Interrupt Status<br>LocalInt<br>Spare<br>RefTxClockLock<br>BurstInIdle<br>BurstOutIdle<br>TxIdleState<br>RxIdleState<br>RxFifoOverFlowLat<br>TxUDoneLat<br>RXUDoneLat<br>RXUDoneLat<br>RXUDoneLat<br>RXUDoneLat<br>Read DMA Interrupt Occurred<br>Write DMA Interrupt Occurred<br>Write DMA Interrupt Occurred<br>Write DMA Error Occurred<br>Read DMA Error Occurred<br>Read DMA Error Occurred<br>RxAFLvIIntLat<br>TxAELvIIntLat<br>RxAfIInt<br>TxAmtInt<br>Spare<br>Rx FIFO Full |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                                                                                                                                           | RxAfIInt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 5                                                                                                                                           | Rx FIFO Almost Full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4                                                                                                                                           | Rx FIFO Empty<br>Spare                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3<br>2                                                                                                                                      | Tx FIFO Full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| -                                                                                                                                           | Tx FIFO Almost Empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0                                                                                                                                           | Tx FIFO Empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

FIGURE 14

PCI-NECL2-RTN10 CHANNEL STATUS PORT

TX FIFO Status: Tx FIFO Empty is set when the entire allocated chain is empty. When '0' there is at least one data point within the chain. TX DMA FIFO[511x32] => SDRAM[programmable] => SDRAM TX IO FIFO[511x32] => TX IO FIFO[16Kx32].

Tx Almost Empty when set ['1'] means there are fewer LW's within the programmed TX

memory chain than the Programmed Almost Empty level. Please note: this is a less than comparison. '0' means there are more than or equal to the programmed level within the memory chain.

Tx FIFO Full is set when the Tx DMA FIFO is full. '0' means there is at least 1 location open.

RX FIFO Status: RX DMA FIFO[511x32] <= SDRAM[programmable] <= SDRAM RX IO FIFO[511x32] <= RX IO FIFO[16Kx32].

Rx FIFO Empty is set when the Rx DMA FIFO is empty. When '0' there is at least one data point within the Rx DMA FIFO.

Rx Almost Full when set ['1'] means there are more LW's within the programmed RX memory chain than the Programmed Almost Full level. Please note: this is a greater/equal comparison. '0' means there are less than the programmed level within the memory chain.

Rx FIFO Full is set when the Rx DMA FIFO is full. '0' means there is at least 1 location open.

Please note with the Rx side status; the status reflects the state of the FIFO and does not take the 4 deep pipeline into account. For example the FIFO may be empty and there may be valid data within the pipeline. The data count with the combined FIFO and pipeline value and can also be used for read size control. [see later in register descriptions]

<u>RxFifoOverFlowLat</u>: When a one is read, an error has been detected. This will occur if FIFO is full when the loader function tries to write to it. A zero indicates that no error has occurred. This bit is latched and can be cleared by writing back to the Status register with a one in the appropriate bit position.

<u>Write/Read DMA Error Occurred</u>: When a one is read, a write or read DMA error has been detected. This will occur if there is a target or master abort or if the direction bit in the next pointer of one of the chaining descriptors is incorrect. A zero indicates that no write or read DMA error has occurred. These bits are latched and can be cleared by writing back to the Status register with a one in the appropriate bit position.

<u>Write/Read DMA Interrupt Occurred</u>: When a one is read, a write/read DMA interrupt is latched. This indicates that the scatter-gather list for the current write or read DMA has completed, but the associated interrupt has yet to be processed. A zero indicates that no write or read DMA interrupt is pending.

<u>Tx IDLE</u> is set when the state-machine is in the idle state. When lower clock rates are used it may take a while to clean-up and return to the idle state. If SW has cleared the start bit to terminate the data transfer; SW can use the IDLE bit to determine when the HW has completed its task and returned.

<u>**Rx IDLE</u></u> is set when the state-machine is in the idle state. When lower clock rates are used it may take a while to clean-up and return to the idle state. If SW has cleared the start bit to terminate the transfer; SW can use the IDLE bit to determine when the HW has completed its task and returned. For RTN10 this is the inverted DataEnable – when '0' data is being received and when '1' no data is being received.</u>**

<u>BO and BI Idle</u> are Burst Out and Burst In IDLE state status for the Receive and Transmit DMA actions. The bits will be 1 when in the IDLE state and 0 when processing a DMA. A new DMA should not be launched until the State machine is back in the IDLE state. Please note that the direction implied in the name has to do with the DMA direction – Burst data into the card for Transmit and burst data out of the card for Receive.

<u>Local Interrupt</u> is the masked combined interrupt status for the channel not including DMA. The status is before the master interrupt enable for the channel.

Interrupt Status is the combined Local Interrupt with DMA and the master interrupt enable. If this bit is set this channel has a pending interrupt request.

<u>RxAFLvIIntLat</u>: When set the Rx Data FIFO has become almost Full based on the programmed count. The software can do a looped read or use DMA to retrieve the programmed count amount of data from the storage FIFO. The signal is latched and can be cleared via write back with this bit set. The signal can be used to generate an interrupt if desired.

<u>TxAELvIIntLat</u>: When set the Tx Data FIFO has become almost Empty based on the programmed count. The software can do a looped write or use DMA to load the programmed count amount of data to the storage FIFO. The signal is latched and can be cleared via write back with this bit set. The signal can be used to generate an interrupt if desired.

<u>TxUDoneLat</u>, <u>RxUDoneLat</u> should be treated as "don't care" for STE3. These bits apply to the retransmit modes designed into the SDRAM controller and not used for STE3.

<u>TxCompletedLat</u> When set '1' indicates the SM has completed a transfer – the FIFO has gone empty and the data transferred. This is a sticky bit cleared by writing back with the same bit set. This bit is anded with the transmit interrupt enable to create an interrupt request if desired.

<u>RefTxClockLock</u> when '1' indicates the DCM used to generate the internal transmit clocks has achieved locked status with the received reference clock. This bit must be set prior to resetting the transmit FIFO as part of initialization.

## RTN10\_CHAN\_WR\_DMA\_PNTR

[0x8] Write DMA Pointer (write only) BurstIn DMA Pointer Address Register

| Data Bit | Description                                |

|----------|--------------------------------------------|

| 31-2     | First Chaining Descriptor Physical Address |

| 1        | direction [0]                              |

| 0        | end of chain                               |

|          |                                            |

FIGURE 15

PCI-NECL2-RTN10 WRITE DMA POINTER REGISTER

This write-only port is used to initiate a scatter-gather write [TX] DMA. When the address of the first chaining descriptor is written to this port, the DMA engine reads three successive long words beginning at that address. Essentially this data acts like a chaining descriptor value pointing to the next value in the chain.

The first is the address of the first memory block of the DMA buffer containing the data to read into the device, the second is the length in bytes of that block, and the third is the address of the next chaining descriptor in the list of buffer memory blocks. This process is continued until the end-of-chain bit in one of the next pointer values read indicates that it is the last chaining descriptor in the list.

All three values are on LW boundaries and are LW in size. Addresses for successive parameters are incremented. The addresses are physical addresses the HW will use on the PCI bus to access the Host memory for the next descriptor or to read the data to be transmitted. In most OS you will need to convert from virtual to physical. The length parameter is a number of bytes, and must be on a LW divisible number of bytes.

Status for the DMA activity can be found in the channel control register and channel status register.

Notes:

- 1. Writing a zero to this port will abort a write DMA in progress.

- 2. End of chain should not be set for the address written to the DMA Pointer Address Register. End of chain should be set when the descriptor follows the last length parameter.

- 3. The Direction should be set to '0' for Burst In DMA in all chaining descriptor locations.

## RTN10\_CHAN\_TX\_FIFO\_COUNT

[0x8] TX FIFO data count (read only) TX FIFO Data Count Port

Data BitDescription31-0TX Data Words Stored

FIGURE 16

PCI-NECL2-RTN10 TX FIFO DATA COUNT PORT

This read-only register port reports the number of 32-bit data words in the Transmit FIFO. This design has a variable number of locations possible due to the programmable ranges for the TX and RX functions. 0 extended to a 32 bit value. The SDRAM module contains FIFO's with 32/16 and 16/32 size ports. Due to the way Xilinx FPGA FIFO's are implemented the x16 count can be ½ word different from the 32 bit count. Since the SDRAM is x16 the three counts are added, synchronized and shifted to present the x32 count to the system. The count read may be 1 fewer than actually stored in memory under certain conditions.

Maximum TX memory is 511[SDRAM DMA FIFO] + 511 [SDRAM IO FIFO] + 8M if all of the SDRAM is allocated to the TX process + 16K-1 [TX IO FIFO]

## RTN10\_CHAN\_RD\_DMA\_PNTR

[0xC] Read DMA Pointer (write only) BurstIn DMA Pointer Address Register

| Data Bit | Description                                |

|----------|--------------------------------------------|

| 31-2     | First Chaining Descriptor Physical Address |

| 1        | direction [1]                              |

| 0        | end of chain                               |

|          |                                            |

FIGURE 17

PCI-NECL2-RTN10 READ DMA POINTER REGISTER

This write-only port is used to initiate a scatter-gather read [RX] DMA. When the address of the first chaining descriptor is written to this port, the DMA engine reads three successive long words beginning at that address. Essentially this data acts like a chaining descriptor value pointing to the next value in the chain.

The first is the address of the first memory block of the DMA buffer to write data from the device to, the second is the length in bytes of that block, and the third is the address of the next chaining descriptor in the list of buffer memory blocks. This process is continued until the end-of-chain bit in one of the next pointer values read indicates that it is the last chaining descriptor in the list.

All three values are on LW boundaries and are LW in size. Addresses for successive parameters are incremented. The addresses are physical addresses the HW will use on the PCI bus to access the Host memory for the next descriptor or to read the data to be transmitted. In most OS you will need to convert from virtual to physical. The length parameter is a number of bytes, and must be on a LW divisible number of bytes.

Status for the DMA activity can be found in the channel control register and channel status register.

Notes:

- 1. Writing a zero to this port will abort a write DMA in progress.

- 2. End of chain should not be set for the address written to the DMA Pointer Address Register. End of chain should be set when the descriptor follows the last length parameter.

- 3. The Direction should be set to '1' for Burst Out DMA in all chaining descriptor locations.

## RTN10\_CHAN\_RX\_FIFO\_COUNT

[0xC] RX FIFO data count (read only) RX FIFO Data Count Port

Data BitDescription31-0RX Data Words Stored

FIGURE 18

PCI-NECL2-RTN10 TX FIFO DATA COUNT PORT

This read-only register port reports the number of 32-bit data words in the Receive FIFO. This design has a variable number of locations possible due to the programmable ranges for the TX and RX functions. 0 extended to a 32 bit value. The SDRAM module contains FIFO's with 32/16 and 16/32 size ports. Due to the way Xilinx FPGA FIFO's are implemented the x16 count can be ½ word different from the 32 bit count. Since the SDRAM is x16, the three counts are added, synchronized and shifted to present the x32 count to the system. The count read may be 1 fewer than actually stored in memory under certain conditions.

Maximum RX memory is 511[SDRAM DMA FIFO] + 511 [SDRAM IO FIFO] + 8M + DMA Pipeline [4] if all of the SDRAM is allocated to the RX process + 16K-1[Rx IO FIFO]

#### RTN10\_CHAN\_FIFO

[0x10] Write TX/Read RX FIFO Port **RX and TX FIFO Port**

Data BitDescription31-0FIFO data word

FIGURE 19

PCI-NECL2-RTN10 RX/TX FIFO PORT

This port is used to make single-word accesses to and from the FIFO. Data read from this port will no longer be available for DMA transfers. Writing to the port loads the Tx FIFO, Reading unloads the Rx FIFO.

#### RTN10\_CHAN\_TX\_AMT\_LVL

[0x14] Tx almost-empty level (read/write) Tx Almost-Full Level Register

| Data Bit | Description                |

|----------|----------------------------|

| 31-0     | Tx FIFO Almost-Empty Level |

|          |                            |

FIGURE 20

PCI-NECL2-RTN10 TX ALMOST EMPTY LEVEL REGISTER

This read/write port accesses the almost-empty level register. When the number of data words in the transmit data FIFO is less than than this value, the almost-empty status bit will be set. The register is R/W for 32 bits. The mask is valid for a size matching the depth of the FIFO. The count is based on the total memory allocated in the SDRAM memory chain.

### RTN10\_CHAN\_RX\_AFL\_LVL

[0x18] Rx almost-full (read/write) Rx Almost-Full Level Register

| Data Bit | Description               |

|----------|---------------------------|

| 31-0     | Rx FIFO Almost-Full Level |

FIGURE 21

PCI-NECL2-RTN10 RX ALMOST FULL LEVEL REGISTER

This read/write port accesses the almost-full level register. When the number of data words in the receive data FIFO is equal or greater than this value, the almost-full status bit will be set. The register is R/W for 32 bits. The mask is valid for a size matching the depth of the FIFO. The count is based on the total memory allocated in the SDRAM memory chain. The level includes the pipeline for an additional 4 locations.

### RTN10\_CHAN\_TX

[0x1C] Channel Transmit Control Register (read/write) Channel TX Control Register

| Data Bit | Description       |

|----------|-------------------|

| 31-18    | Spare             |

| 17       | ClkInv            |

| 16-10    | Spare             |

| 9        | EnTxUnLoad        |

| 8        | EnTxLoad          |

| 7        | spare             |

| 6        | TxFifoAmtIntEnLvI |

| 5        | spare             |

| 4        | TxUnFIIntEn       |

| 3        | TxAEIntEn         |

| 2        | TxIntEn           |

| 1        | spare             |

| 0        | TxEn              |

|          |                   |

FIGURE 22 PCI-NECL2-RTN10 CHANNEL TRANSMIT CONTROL REGISTER

Set spare bits to '0'.

TxEn when set causes the Transmit State Machine to begin operation. When the Transmitter state-machine has determined that Data is in the Transmit FIFO, and sufficient data is available transmission will begin. Clearing TxEn will return the State Machine to the idle state. Please note: for the case where transmission has started, and data in the local FIFO [IO] is not present but data is present in the SDRAM chain, transmission will restart without waiting for the READY threshold.

TxIntEn when set enables the transmitter to generate an interrupt when the transmitter has run dry and returned to the idle state. Please note the enable is not self clearing, adding data to the FIFO will retrigger the state machine unless software removes the enable. The IDLE state will not be reached unless the entire chain is emptied.

TxAEIntEn when set enables the interrupt based on the TX FIFO Almost Empty flag. When the interrupt occurs a programmable amount of data can be stored into the FIFO making for an efficient DMA or burst of writes to load the FIFO.

EnTxLoad and EnTxUnLoad when set enable the SDRAM state-machine to operate in the TX section of SDRAM. UnLoad is the function of taking data from the SDRAM and moving to the IO FIFO. Load is the function of taking data from the DMA FIFO and

writing to the SDRAM. When using the retransmit modes in memory the unload function can be left disabled until the pattern is loaded and then enabled. For FIFO mode both enables can be set together.

**ClkInv** when set inverts the transmit reference clock to have the data stable on the rising edge. Default is stable on the falling edge.

### RTN10\_CHAN\_TX\_READY\_REG

[0x2C] Tx hold off (read/write) Rx Almost-Full Level Register

| Data Bit | Description       |

|----------|-------------------|

| 31-0     | Hold Off LW Count |

FIGURE 23

PCI-NECL2-RTN10 TX HOLD OFF REGISTER

This read/write port is used to set a minimum threshold of data to be in the TX Statemachine local FIFO before the State-Machine starts transmission. By programming this register to a non-zero amount the start and DMA start are decoupled somewhat.

Setting the level to 100 LW, and the TX enabled before starting the DMA function will allow 100 LW to accumulate in the IO local buffer before enable is set and data is transmitted. This gives the DMA function a head start and will allow the data transfer to be done in one contiguous transfer. Your system may require larger or smaller settings. Only the TX IO FIFO is used to compare against the programmed count [ equal or greater] => the maximum is 16K-1. Do not set for more than the intended data size. Remember this is in LW; if you are thinking in bytes, divide by 4.

If having the enable set and disabled a few times during start-up does not affect your application the count can be set to 0. During DMA start-up the system may break the first segments into small transfers causing the FIFO to only load 1 LW [4 bytes] several times before the DMA really gets going. This is an OS dependent phenomenon.

### RTN10\_CHAN\_RX

[0x34] Channel RX Control Register (read/write) Channel Control Register

| Data Bit<br>17<br>16 | Description<br>ClkInv<br>FrameIgnore |

|----------------------|--------------------------------------|

| 15-10                | spare                                |

| 9                    | EnRxUnLoad                           |

| 8                    | EnRxLoad                             |

| 7                    | spare                                |

| 6                    | RxFifoAflIntEnLvI                    |

| 5                    | spare                                |

| 4                    | RxFifoOvFIIntEn                      |

| 3                    | RxFifoAFIntEn                        |

| 2                    | RxIntEn                              |

| 1                    | spare                                |

| 0                    | RxEn                                 |

|                      |                                      |

| FIG | URE | 24       |

|-----|-----|----------|

|     | 0.0 | <u> </u> |

PCI-NECL2-RTN10 CHANNEL RX CONTROL REGISTER

RxEn when set causes the Rx State Machine to begin operation. The receiver uses the free running reference clock and looks for the enable signal to be in the active state when the falling edge of the clock is received. With each active clock [falling edge and enable set] data is captured [byte] and stored into a local FIFO. The data is converted to 32 bit words. The data is stored LSB first MSB last. Data is continued to be captured until RxEn is disabled ['0']. When disabled the receiver is disabled and the pointer for the first byte captured returned to the 00 location.

RxIntEn when set enables the completion of the Rx SDRAM loop to cause an interrupt. Unused in RTN10. Set to '0'.

RxFifoAFIntEn when set enables the interrupt based on the Rx FIFO Almost Full flag. When the interrupt occurs a programmable amount of data can be read from the FIFO making for an efficient DMA read or burst of reads to unload the FIFO. Please see the programmable definition for the Almost Full Flag.

<u>RxFifoOvFIIEn</u> when set enables the interrupt based on the Rx FIFO OverFlow condition. When the State-machine writes to the FIFO the status is tested. If the FIFO is full when time to write the OverFlow status is set. If the interrupt is enabled the status is gated out to drive the interrupt request to the host.

The local IO FIFO data is transferred to the SDRAM RX IO FIFO automatically. For the

full condition to happen the entire defined "FIFO" path would need to be filled.

<u>EnRxLoad and EnRxUnLoad</u> when set enable the SDRAM state-machine to operate in the RX section of SDRAM. UnLoad is the function of taking data from the SDRAM and moving to the DMA FIFO. Load is the function of taking data from the IO FIFO and writing to the SDRAM. When using the retransmit modes in memory the unload function can be left disabled until the pattern is loaded and then enabled. For FIFO mode both enables can be set together.

While it is unlikely that the RX retransmit function would be used, it can be used as a self generating data stream for testing system operation. Due to schedule requirements this function has not been tested for RTN10.

**FrameIgnore** When set causes the receiver to ignore the received enable signal and only qualify data with the received clock. Default is to use the framing to prevent capture of unwanted data.

**ClkInv** when set causes the receiver to use the rising edge to capture data. Default is to use the falling edge to capture data.

**Rx and Tx Memory Definitions.** The SDRAM is a block of memory comprised of banks and pages. The hardware flattens the memory into one large page – that is the handling of the memory is hidden from the SW definitions. The SW can partition the memory into an RX and a TX segment or one large RX or TX segment or neither depending on the settings for the bypass, Load and UnLoad, plus memory address definitions.

The next set of registers is used to set the addresses to be used for the memory. The addresses are inclusive. For example setting Mem A = 0x00 will start the memory at 0x00. Setting MemD 0 0x10 will use address 0x10 as the last address in the segment.

For "normal" bidirectional operation the start, middle,and end of memory would be used to separate the Rx and Tx spaces.

$Tx = 0x000000 \Leftrightarrow 0x7FFFFF : MemA = 0x000000, MemD = 0x7FFFFF Rx = 0x800000 \Leftrightarrow 0xFFFFFF : MemA = 0x800000, MemD = 0xFFFFFF$

Setting the control bits for FIFO operation will result in two large FIFO's with 1/2 the memory allocated to each. Asymmetrical memory allocation is fine too.

Each of the locations is 16 bits or 2 bytes => 16 Mbytes per FIFO in the example case.

### RTN10\_CHAN\_RX\_MEM\_A

[0x50] Rx Memory A offset definition (read/write) **Rx Memory Definition**

| Data Bit | Description |

|----------|-------------|

| 31-0     | RX Memory A |

FIGURE 25

PCI-NECL2-RTN10 RX MEMORY A REGISTER

The primary use of this port is to set the initial address of the RX segment of the SDRAM memory. The address is a word boundary and should be set to a LW boundary 0,4,8 etc. This is channel 0 within the SDRAM module.

For initialization the register should be set to x37 for loading to the SDRAM control register. Once initialization is complete the register should be set to the memory definition prior to enabling in the RX state-machine control register. See Base control register for initialization control.

### RTN10\_CHAN\_TX\_MEM\_A

[0x54] Tx Memory A offset definition (read/write) **Tx Memory Definition**

| Data Bit | Description |

|----------|-------------|

| 31-0     | TX Memory A |

FIGURE 26

PCI-NECL2-RTN10 TX MEMORY A REGISTER

The primary use of this port is to set the initial address of the TX segment of the SDRAM memory. The address is a word boundary and should be set to a LW boundary 0,4,8 etc. This is channel 1 within the SDRAM module.

Be sure to set the memory segments to discrete spaces, the controller does not check for overlapping definitions and you will get "interesting" results if you try this.

Embedded Solutions

### RTN10\_CHAN\_SET\_MEM