## DYNAMIC ENGINEERING

150 DuBois St., Suite C, Santa Cruz, CA 95060 831-457-8891 Fax 831-457-4793 http://www.dyneng.com sales@dyneng.com Est. 1988

# User Manual IP-Parallel-IO

Digital Parallel Interface IP Module

| 48 TTL / 0 485  | –TTL       |

|-----------------|------------|

| 40 TTL / 4 485  | <b>–</b> 1 |

| 32 TTL / 8 485  | <b>-2</b>  |

| 24 TTL / 12 485 | <b>-</b> 3 |

| 16 TTL / 16 485 | <b>-4</b>  |

| 8 TTL / 20 485  | <b>–</b> 5 |

| 0 TTL / 24 485  | -485       |

Revision J1 6/30/17 Corresponding Hardware: Revision 03 Fab number: 10-2001-0103

## **IP-Parallel-IO**

Digital Parallel Interface IP Module

## **Dynamic Engineering**

150 DuBois St., Suite C Santa Cruz, CA 95060 831-457-8891 831-457-4793 FAX www.dyneng.com

This document contains information of proprietary interest to Dynamic Engineering. It has been supplied in confidence and the recipient, by accepting this material, agrees that the subject matter will not be copied or reproduced, in whole or in part, nor its contents revealed in any manner or to any person except to meet the purpose for which it was delivered.

Dynamic Engineering has made every effort to ensure that this manual is accurate and complete. Still, the company reserves the right to make improvements or changes in the product described in this document at any time and without notice. Furthermore, Dynamic Engineering assumes no liability arising out of the application or use of the device described herein.

The electronic equipment described herein generates, uses, and can radiate radio frequency energy. Operation of this equipment in a residential area is likely to cause radio interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Dynamic Engineering's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Dynamic Engineering.

This product has been designed to operate with IP Module carriers and compatible user-provided equipment. Connection of incompatible hardware is likely to cause serious damage.

©2000-2017 by Dynamic Engineering.

Other trademarks and registered trademarks are owned by their respective manufactures.

## **Table of Contents**

| Product Description and Operation            | <b></b> 7 |

|----------------------------------------------|-----------|

| Programming                                  |           |

| Register Definition                          |           |

| CNTL0-TTL:                                   | 13<br>15  |

| CNTLO-TTL. CNTL1-TTL                         | 15        |

| CNTL2-TTL                                    | 15        |

| CNTL0-1                                      | 16        |

| CNTL1-1                                      | 16        |

| CNTL2-1                                      | 16        |

| CNTL0-2                                      | 17        |

| CNTL1-2                                      | 17        |

| CNTL2-2                                      | 17        |

| CNTL0-3                                      | 18        |

| CNTL1-3                                      | 18        |

| CNTL2-3                                      | 18        |

| CNTL0-4                                      | 19        |

| CNTL1-4                                      | 19        |

| CNTL2-4                                      | 19        |

| CNTL0-5                                      | 20        |

| CNTL1-5                                      | 20        |

| CNTL2-5                                      | 20        |

| CNTL0-485                                    | 21        |

| CNTL1-485                                    | 21        |

| CNTL2-485                                    | 21        |

| Bit Mapping Tables                           | 22        |

| Base_CNTL                                    | 23        |

| INTerrupt Enable                             | 25        |

| INTerrupt Edge_Lvl                           | 26        |

| INTerrupt Polarity                           | 27        |

| Data Input Filtered                          | 28        |

| Data Input Direct                            | 29        |

| Pre-Load Registers                           | 30        |

| Mask Registers<br>Read-Back Registers        | 31<br>32  |

| Status Register                              | 34        |

| BIS VECTOR                                   | 34<br>34  |

| Interrupts                                   |           |

| •                                            |           |

| ID PROM                                      |           |

| IP-Parallel-x Logic Interface Pin Assignment |           |

| IP-Parallel-IO Interface Pin Assignment      | 38        |

| IP-Parallel-1 Interface Pin Assignment       | 39        |

| IP-Parallel-2 Interface Pin Assignment   | 40 |

|------------------------------------------|----|

| IP-Parallel-3 Interface Pin Assignment   | 41 |

| IP-Parallel-4 Interface Pin Assignment   |    |

| IP-Parallel-5 Interface Pin Assignment   |    |

| IP-Parallel-485 Interface Pin Assignment |    |

| Applications Guide                       | 45 |

| Interfacing                              | 45 |

| Loop-back Connections                    | 47 |

| Construction and Reliability             |    |

| Thermal Considerations                   | 53 |

| Warranty and Repair                      | 53 |

| Service Policy                           | 53 |

| Out of Warranty Repairs                  | 53 |

| For Service Contact:                     |    |

| Specifications                           | 54 |

| Order Information                        | 55 |

## List of Figures

| FIGURE 1   | IP-PARALLEL-IO INTERNAL ADDRESS MAP           | 13 |

|------------|-----------------------------------------------|----|

|            | TL IP-PARALLEL-TTL CONTROL REGISTER 0 BIT MAP | 15 |

|            | TL IP-PARALLEL-TTL CONTROL REGISTER 1 BIT MAP | 15 |

| FIGURE 4-T |                                               | 15 |

|            | IP-PARALLEL-1 CONTROL REGISTER 0 BIT MAP      | 16 |

| FIGURE 3-1 |                                               | 16 |

| FIGURE 4-1 |                                               | 16 |

| FIGURE 2-2 |                                               | 17 |

| FIGURE 3-2 |                                               | 17 |

| FIGURE 4-2 | IP-PARALLEL-2 CONTROL REGISTER 2 BIT MAP      | 17 |

| FIGURE 2-3 | IP-PARALLEL-3 CONTROL REGISTER 0 BIT MAP      | 18 |

| FIGURE 3-3 | IP-PARALLEL-3 CONTROL REGISTER 1 BIT MAP      | 18 |

| FIGURE 4-3 | IP-PARALLEL-3 CONTROL REGISTER 2 BIT MAP      | 18 |

| FIGURE 2-4 | IP-PARALLEL-4 CONTROL REGISTER 0 BIT MAP      | 19 |

| FIGURE 3-4 | IP-PARALLEL-4 CONTROL REGISTER 1 BIT MAP      | 19 |

| FIGURE 4-4 | IP-PARALLEL-4 CONTROL REGISTER 2 BIT MAP      | 19 |

| FIGURE 2-5 | IP-PARALLEL-5 CONTROL REGISTER 0 BIT MAP      | 20 |

| FIGURE 3-5 | IP-PARALLEL-5 CONTROL REGISTER 1 BIT MAP      | 20 |

|            | IP-PARALLEL-5 CONTROL REGISTER 2 BIT MAP      | 20 |

|            | 85 IP-PARALLEL-485 CONTROL REGISTER 0 BIT MAP | 21 |

| FIGURE 3-4 |                                               | 21 |

|            | 85 IP-PARALLEL-485 CONTROL REGISTER 2 BIT MAP | 21 |

| FIGURE 5   |                                               | 23 |

| FIGURE 6   | IP-PARALLEL-IO INTERRUPT ENABLE 0 BIT MAP     | 25 |

| FIGURE 7   | IP-PARALLEL-IO INTERRUPT ENABLE 1 BIT MAP     | 25 |

| FIGURE 8   | IP-PARALLEL-IO INTERRUPT ENABLE 2 BIT MAP     | 25 |

| FIGURE 9   | IP-PARALLEL-IO INTERRUPT EDG_LVL 0 BIT MAP    | 26 |

| FIGURE 10  | IP-PARALLEL-IO INTERRUPT EDG_LVL 1 BIT MAP    | 26 |

|            | IP-PARALLEL-IO INTERRUPT EDG_LVL 2 BIT MAP    | 26 |

|            | IP-PARALLEL-IO INTERRUPT POL 0 BIT MAP        | 27 |

| FIGURE 13  | IP-PARALLEL-IO INTERRUPT POL 1 BIT MAP        | 27 |

| FIGURE 14  | IP-PARALLEL-IO INTERRUPT POL 2 BIT MAP        | 27 |

| FIGURE 15  | IP-PARALLEL-IO INTERRUPT DATAIN_FIL0 BIT MAP  | 28 |

| FIGURE 16  | IP-PARALLEL-IO INTERRUPT DATAIN_FIL1 BIT MAP  | 28 |

| FIGURE 17  | IP-PARALLEL-IO INTERRUPT DATAIN_FIL2 BIT MAP  | 28 |

| FIGURE 18  | IP-PARALLEL-IO INTERRUPT DATAIN_DIR0 BIT MAP  | 29 |

| FIGURE 19  | IP-PARALLEL-IO INTERRUPT DATAIN_DIR1 BIT MAP  | 29 |

| FIGURE 20  | IP-PARALLEL-IO INTERRUPT DATAIN_DIR2 BIT MAP  | 29 |

| FIGURE 21  | IP-PARALLEL-IO PRE-LOAD LOWER BIT MAP         | 30 |

| FIGURE 22  | IP-PARALLEL-IO PRE-LOAD UPPER BIT MAP         | 30 |

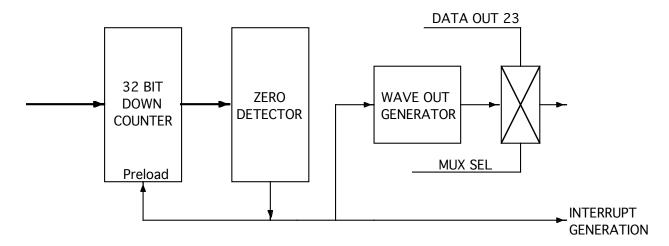

| FIGURE 23  | IP-PARALLEL-IO COUNTER/TIMER A                | 31 |

| FIGURE 24  | IP-PARALLEL-IO MASK LOWER BIT MAP             | 31 |

| FIGURE 25  | IP-PARALLEL-IO MASK UPPER BIT MAP             | 31 |

| FIGURE 26  | IP-PARALLEL-IO READ-BACK LOWER BIT MAP        | 32 |

| FIGURE 27 | IP-PARALLEL-IO READ-BACK UPPER BIT MAP | 32 |

|-----------|----------------------------------------|----|

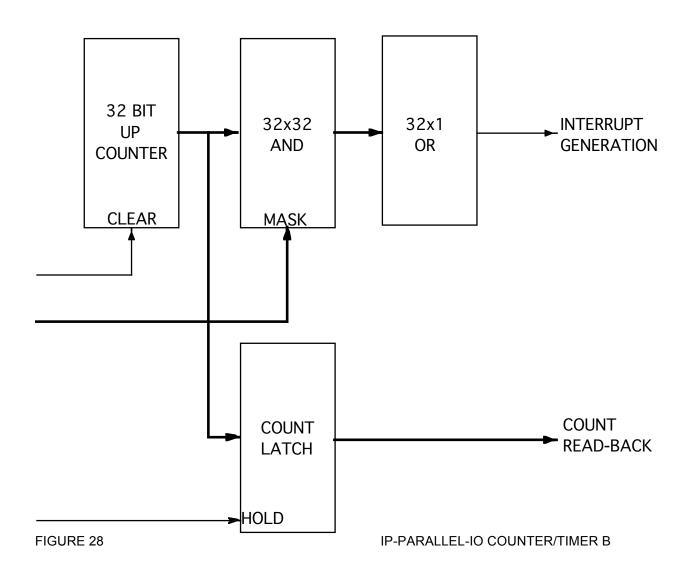

| FIGURE 28 | IP-PARALLEL-IO COUNTER/TIMER B         | 33 |

| FIGURE 29 | IP-PARALLEL-IO STATUS BIT MAP          | 34 |

| FIGURE 30 | IP-PARALLEL-IO ID PROM                 | 36 |

| FIGURE 31 | IP-PARALLEL-IO LOGIC INTERFACE         | 37 |

| FIGURE 32 | IP-PARALLEL-IO IO INTERFACE            | 38 |

| FIGURE 33 | IP-PARALLEL-1 IO INTERFACE             | 39 |

| FIGURE 34 | IP-PARALLEL-2 IO INTERFACE             | 40 |

| FIGURE 35 | IP-PARALLEL-3 IO INTERFACE             | 41 |

| FIGURE 36 | IP-PARALLEL-4 IO INTERFACE             | 42 |

| FIGURE 37 | IP-PARALLEL-5 IO INTERFACE             | 43 |

| FIGURE 38 | IP-PARALLEL-485 IO INTERFACE           | 44 |

|           |                                        |    |

## **Product Description and Operation**

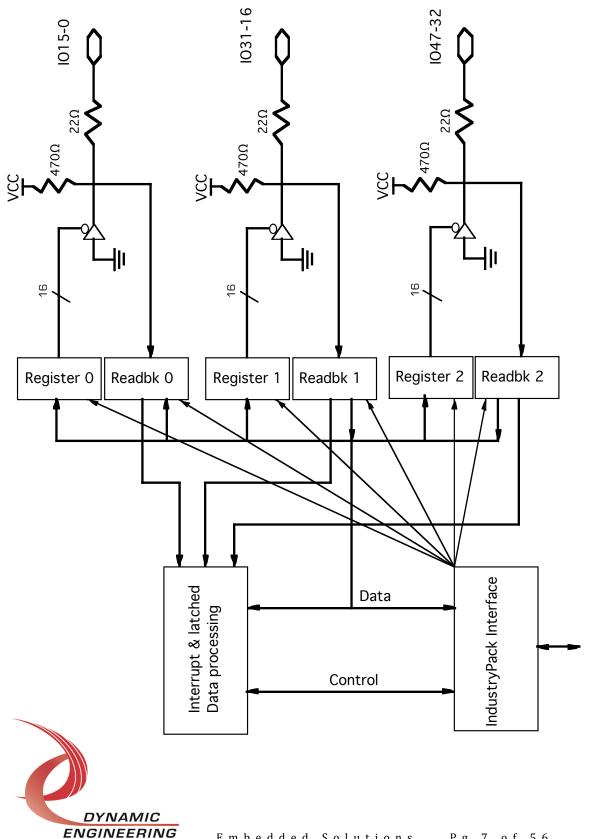

IP-Parallel-IO is part of the IP Module family of modular I/O components. IP-Parallel-IO

is capable of providing multiple protocols. The TTL version provides 48 uncommitted IO. Each channel can be programmed to be input, output and interrupter. The 485 version has 24 differential pairs. TTL and Differential pairs can be mixed to have any combination of TTL and Differential IO. Please refer to the ordering table to see the standard IO options.

Each TTL bit has a register bit associated with it. When the register bit is set to '0' that channel turns on the open-drain driver and puts a '0' on the line. When the register bit is set to '1' then the open drain driver is turned off and the pull-up will create a high level on the line unless some other system element is driving the line low. The register is read-write and will always return the value written to it. There are 48 IO lines. Three 16 bit wide registers are dedicated to the Control [CNTL] bus.

The CNTL bus is supported by a synchronization control bit in the base register. The control registers are double buffered with the second register level connected to the IO. The synchronization bit enables the second level registers to update or hold. Clearing the enable before updating and re-enabling after the primary registers have new values will allow the 48 IO to be synchronously updated through the second level of registers. If left enabled the CNTL will be updated one clock after the register is updated. If disabled, then the last enabled control setting is held. The reset default is 'FFFFFFFFFF' to turn the drivers off in TTL mode.

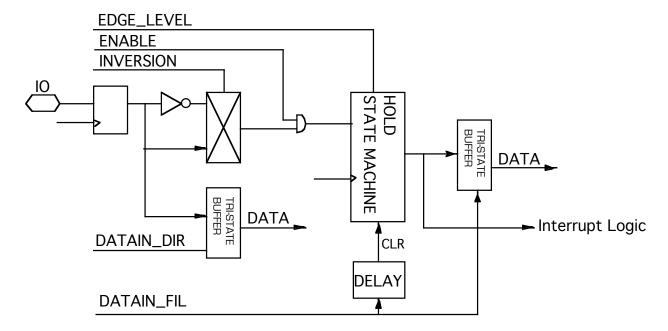

Each IO line is also brought into the FPGA [Xilinx Spartan II]. The IO lines are available as a direct read or after filtering. The data read from the IO will match the register bits if there are no other drivers in the system. The IO bits may not match if an external device is attached.

Each channel has an enable, sense, and edge or level bit associated with it. The enable will block or enable a particular channel from being received into the filtered logic. The sense will either keep the current version or invert the data received. The edge or level control will make the hold circuit wait for an edge from 0 > 1 or react to a level. The hold circuit captures data and holds it until read. The data is registered at the chip edge, and again after the enable and inversion circuitry. Each bit has a separate hold circuit. If a signal is detected high then the signal is held until the data is read. With the inversion capability each channel can be programmed to "be high" or to transition to a high condition when the channel has something of interest.

The registers are referenced to the IP clock and operate at 8 or 32 MHz depending on the slot configuration. Each group of 16 channels has a separate read clear signal. The channels can be read in any order and not loose data. The circuit will capture pulses down to 2 reference clocks wide. 62.5 nS or 250 nS with the standard IP reference clock.

The active high signals are combined to create an interrupt request based on the captured and held data. If the master interrupt enable is "enabled" the interrupt is passed to the system. The interrupt is cleared by reading the data or disabling the master enable. The user can program each channel to use the edge or level condition. The edge is particularly useful for long duration signal where repeated interrupts are not desired. The alternate approach is to flip the sense bit and create an interrupt when the signal has switched to the opposite polarity.

Instruction order is important. Once the interrupt is detected the sense needs to be switched before the interrupt is re-enabled or a second interrupt is likely to be generated. It is recommended to read from the filtered data path after the processing parameters are changed to clear any interrupts that are created by the changing filter parameters.

With each IO line having all three controls plus independent direction a lot of interrupt possibilities exist.

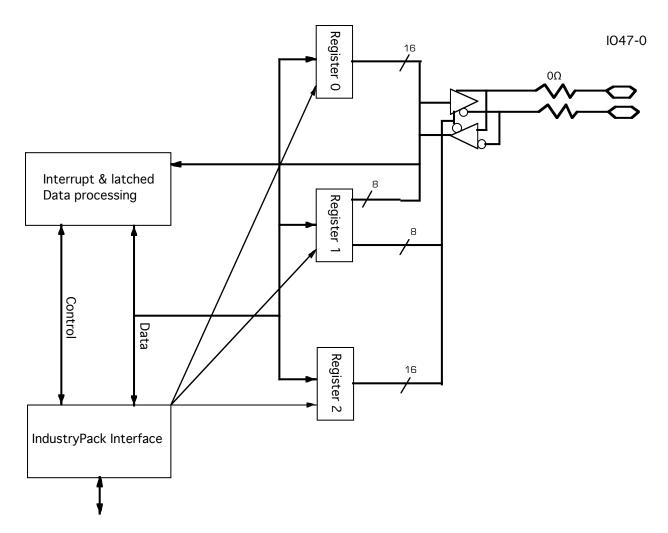

The TTL IO can be substituted with 485 transceivers. Each transceiver uses 2 IO lines for a maximum of 24. The driver and pull-up combination used creates a minimum group of 8 TTL IO or 4 Differential IO to swap. There are 7 standard versions of the board. The TTL version with all TTL IO, the 485 version with all 485 IO and mixed versions with 8, 16, 24, 32, and 40 of the IO dedicated to TTL and the rest with 485 IO. Each FLASH version is populated with a different IDPROM to make card identification easy within your system.

In the versions with 485 transceivers the control bits have an alternate definition. The bits are paired; one the direction control and one the data bit. In the TTL version, all of the bits are data bits. Please refer to the diagram of the -485 version.

When the 485 transceivers are added in place of the TTL drivers, new control definitions occur. For ease of use the control registers are re-mapped between the different versions to group the direction bits and the data bits together at the upper end of the control words [cntl0-2]. The space is divided in half with the upper half used for the control and the lower half for data. In the case with only 485 transceivers the lower 24 bits are data and the upper 24 control. In the –1 case the upper 8 bits are used for 485 with the 40-43 used for data and 44-47 for control. The bits are remapped to the hardware locations within the FPGA. By re-mapping, the data can be written in a natural order if used as a bus. A 0x04 is a 0x04. Without re-mapping, the data bits would be separated by the control bits, and broken into two sections. The groups of 8

are really implemented as two groups of 4. IO47-44 and IO23-20 represent the first group. The re-mapping will put the control and data on cntl40-47. IO47, 45, 23, 21 are the physical control bits. A result of re-mapping the data is normally ordered and more conveniently located. Please refer to the Bit Mapping Table in the programming section.

In addition to the IO version, other custom interfaces are available. Please see our web page for current protocols offered. If you do not find it there, we can redesign the state machines and create a custom interface protocol. That protocol will then be offered as a "standard" special order product. Please contact Dynamic Engineering with your custom application. Several of the IO bits are implemented on the long line clock pins of the FPGA. External clock references can be designed in as a custom option. There is a user oscillator position to support custom state machines and IO requirements. The DMA controls, second interrupt level, and memory space controls are routed to the FPGA to allow for future upgrades.

IP-PARALLEL-IO supports both 8 and 32 Mhz. IP Bus operation. All configuration registers support read and write operations for maximum software convenience. Word operations are supported (please refer to the memory map). The ID, IO, and INT spaces are utilized by the IP-Parallel-IO design.

IP-PARALLEL-IO conforms to the VITA standard. This guarantees compatibility with multiple IP Carrier boards. Because the IP may be mounted on different form factors, while maintaining plug and software compatibility, system prototyping may be done on one IP Carrier board, with final system implementation on a different one. The PCI3IP or PCIe3IP cards make a convenient development platform in many cases. http://www.dyneng.com/pci 3 ip.html, http://www.dyneng.com/PCIe3IP.html

Interrupts are supported by IP-PARALLEL-IO. The interrupt occurs when a programmed transition occurs. The interrupts are individually maskable – each IO channel has a separate mask. The vector is user programmable by a read/write register. The interrupt occurs on IntReq0. The vector can be read in the IO space or automatically with the INT space.

Frequently it is necessary to correlate the time and the event. The IP-Parallel design supports an enhanced MC68230 capability with two - 32 bit counter - timers. The counter-timers are easy to use with a minimum of registers to access and complete independence. The IP clock is used as a reference; both 8 and 32 MHz can be used.

Counter/Timer A features a 32 bit down-counter with a pre-load register. The counter output is tested against a "zero" value. When zero the counter is re-loaded with the pre-load value to create a cycle. At each zero detection an interrupt can be generated. At

each zero detection a waveform can be transitioned. The waveform can be enabled onto the upper data bit.

Counter / Timer B has a 32 bit up counter which can be cleared by the software. The counter output is masked with a user programmable value to select a particular counter bit or bits to use for interrupt creation. The counter output is also available to read via software and can serve as a real-time clock

## Address Map

| Function        |             | Offset                   | Width   | Туре       |

|-----------------|-------------|--------------------------|---------|------------|

| cntl0           | EQU         | \$00                     | word    | read/write |

| cntl1           | EQU         | \$02                     | word    | read/write |

| cntl2           | EQU         | \$04                     | word    | read/write |

| Base_cntl       | EQU         | \$06                     | word    | read/write |

| Int En0         | EQU         | \$08                     | word    | read/write |

| Int En1         | EQU         | \$0A                     | word    | read/write |

| Int En2         | EQU         | \$0C                     | word    | read/write |

| vector          | EQU         | \$0E                     | word    | read/write |

| Int EdgLvI0     | EQU         | \$10                     | word    | read/write |

| Int EdgLvI1     | EQU         | \$12                     | word    | read/write |

| Int EdgLvl2     | EQU         | \$14                     | word    | read/write |

|                 |             |                          |         |            |

| Int Pol0        | EQU         | \$18                     | word    | read/write |

| Int Pol1        | EQU         | \$1A                     | word    | read/write |

| Int Pol2        | EQU         | \$1C                     | word    | read/write |

| status          | EQU         | \$1E                     | word    | read/write |

| dat_in_fil0     | EQU         | \$20                     | word    | read       |

| dat_in_fil1     | EQU         | \$22                     | word    | read       |

| dat_in_fil2     | EQU         | \$24                     | word    | read       |

|                 | <b>5011</b> | 000                      |         |            |

| dat_in_dir0     | EQU         | \$28                     | word    | read       |

| dat_in_dir1     | EQU         | \$2A                     | word    | read       |

| dat_in_dir2     | EQU         | \$2C                     | word    | read       |

| pre_load_l      | EQU         | \$2E                     | word    | read/write |

| pre_load_i      | EQU         | \$30                     | word    | read/write |

| mask I          | EQU         | \$30<br>\$32             | word    | read/write |

| mask u          | EQU         | \$32<br>\$34             | word    | read/write |

| rdbk I          | EQU         | \$3 <del>4</del><br>\$36 | word    | read       |

| rdbk_i          | EQU         | \$38                     | word    | read       |

| Tubk_u          | LQU         | ψυυ                      | WOIG    | Toda       |

| Parallel IDPROM | bvte o      | n word b                 | oundary | read       |

| 3.3             | 2,100       |                          | ···-,   | 1          |

|                 |             |                          |         |            |

## FIGURE 1

IP-PARALLEL-IO INTERNAL ADDRESS MAP

The address map provided is for the local decoding performed within IP-PARALLEL-IO. The addresses are all offsets from a base address. The carrier board that the IP is installed into provides the base address.

## **Programming**

Programming IP-PARALLEL-IO requires only the ability to read and write data in the host's I/O space. The base address is determined by the IP Carrier board.

In order to receive data the software is only required to read from the "Direct" port. Alternatively the filtered data path can be programmed with the enable, Level and edge and then the Filtered data used. If desired, the interrupt can be enabled and the interrupt vector written to the vector register.

A typical sequence would be to first write to the vector register with the desired interrupt vector. Please note that many carrier boards do not use the interrupt vector. The interrupt service routine should be loaded and the mask should be set. The Level and Edge conditions programmed, then the enables set to receive data. The incoming data can be pulsed. The hardware will hold any pulse or level detected until the data is read by software.

Data is written to the Control [cntl] registers. Any active low bits are used to enable the open drain drivers. The drivers have 24 mA sink capability and overcome the pull-up [10 mA] to create a '0' on the bus. A '1' in a bit position turns off the driver leaving the pull-up to set the level to a '1'. Other hardware in the system can also pull the signal line to '0'. If enabled, the lines controlled by the outputs can cause interrupts back to the host. Usually these will be disabled to prevent self-interrupting.

When 485 transceivers are installed the driver section creates a differential signal pair. The pull-up resistors are not installed. A software written '1' will result in the + side driven high and the – side driven to ground. A software written '0' will result in the + side driven to ground and the minus side driven high.

A 32 bit write/read with some carriers will result in two 16 bit accesses to the hardware with automatic incrementing addresses. The 32 bit access is quite a bit faster than a software loop. Dynamic Engineering IP Carriers support 32 bit to 16 bit mapping automatically. The lower 32 bits of the output, "data in filtered", and "data in direct" are on long word boundaries to utilize this feature if available.

Refer to the Theory of Operation section above and the Interrupts section below for more information regarding the exact sequencing and interrupt definitions.

## **Register Definition**

## CNTL0-TTL:

\$00 Parallel Control Register Port read/write

|                         | CONTROL REGISTER 0                                    |  |

|-------------------------|-------------------------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> cntl 15-0 output data control bits |  |

FIGURE 2-TTL

IP-PARALLEL-TTL CONTROL REGISTER 0 BIT MAP

## CNTL1-TTL

\$02 Parallel Control Register Port read/write

|                         | CONTROL REGISTER 1                                     |  |

|-------------------------|--------------------------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> cntl 31-16 output data control bits |  |

FIGURE 3-TTL

IP-PARALLEL-TTL CONTROL REGISTER 1 BIT MAP

#### CNTL2-TTL

\$04 Parallel Control Register Port read/write

|                         | CONTROL REGISTER 2                                     |  |

|-------------------------|--------------------------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> cntl 47-32 output data control bits |  |

FIGURE 4-TTL

IP-PARALLEL-TTL CONTROL REGISTER 2 BIT MAP

- 1. All bits are active low and are reset on power-up. Default to 'FFFF', off state for TTL mode and default to inputs in 485 mode.

- 2. In TTL mode each CNTL bit directly corresponds to an IO bit.

- 3. In mixed and 485 modes the cntl bits are re-mapped to push the 485 definitions to the upper bits, and to separate data and direction.

\$00 Parallel Control Register Port read/write

|                         | CONTROL REGISTER 0                                    |  |

|-------------------------|-------------------------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> cntl 15-0 output data control bits |  |

FIGURE 2-1

IP-PARALLEL-1 CONTROL REGISTER 0 BIT MAP

## CNTL1-1

\$02 Parallel Control Register Port read/write

|                         | CONTROL REGISTER 1                                     |  |

|-------------------------|--------------------------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> cntl 31-16 output data control bits |  |

FIGURE 3-1

IP-PARALLEL-1 CONTROL REGISTER 1 BIT MAP

## CNTL2-1

\$04 Parallel Control Register Port read/write

| CONTROL REGISTER 2 |                                     |                                                                                      |

|--------------------|-------------------------------------|--------------------------------------------------------------------------------------|

| DATA BIT           | DESCRIPTION                         |                                                                                      |

| 7-0                | cntl 39-32 output data control bits |                                                                                      |

| 11-8               | 485 data [IO43-40]                  |                                                                                      |

| 15-12              | 485 direction 1 = TX                |                                                                                      |

|                    | 7-0<br>11-8                         | DATA BIT DESCRIPTION 7-0 cntl 39-32 output data control bits 11-8 485 data [IO43-40] |

FIGURE 4-1

IP-PARALLEL-1 CONTROL REGISTER 2 BIT MAP

- 1. All bits are active low and are reset on power-up. Default to 'FFFF', off state for TTL mode and default to inputs in 485 mode.

- 2. In TTL mode each CNTL bit directly corresponds to an IO bit.

- 3. In mixed and 485 modes the cntl bits are re-mapped to push the 485 definitions to the upper bits, and to separate data and direction.

\$00 Parallel Control Register Port read/write

|                         | CONTROL REGISTER 0                                    |  |

|-------------------------|-------------------------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> cntl 15-0 output data control bits |  |

FIGURE 2-2

IP-PARALLEL-2 CONTROL REGISTER 0 BIT MAP

## CNTL1-2

\$02 Parallel Control Register Port read/write

|   |                         | CONTROL REGISTER 1                                     |  |

|---|-------------------------|--------------------------------------------------------|--|

| С | <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> cntl 31-16 output data control bits |  |

FIGURE 3-2

IP-PARALLEL-2 CONTROL REGISTER 1 BIT MAP

## CNTL2-2

\$04 Parallel Control Register Port read/write

| DATA BIT | DESCRIPTION          |                        |

|----------|----------------------|------------------------|

| 7-0      | 485 data [IO39-32]   |                        |

| 15-8     | 485 direction 1 = TX |                        |

|          | 7-0                  | 7-0 485 data [IO39-32] |

FIGURE 4-2

IP-PARALLEL-2 CONTROL REGISTER 2 BIT MAP

- 1. All bits are active low and are reset on power-up. Default to 'FFFF', off state for TTL mode and default to inputs in 485 mode.

- 2. In TTL mode each CNTL bit directly corresponds to an IO bit.

- 3. In mixed and 485 modes the cntl bits are re-mapped to push the 485 definitions to the upper bits, and to separate data and direction.

\$00 Parallel Control Register Port read/write

| CONTROL REGISTER 0      |                                                       |  |

|-------------------------|-------------------------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> cntl 15-0 output data control bits |  |

FIGURE 2-3

IP-PARALLEL-3 CONTROL REGISTER 0 BIT MAP

#### CNTL1-3

\$02 Parallel Control Register Port read/write

|                     | CONTROL REGISTER 1                              |  |

|---------------------|-------------------------------------------------|--|

| <b>DATA BIT</b> 7-0 | DESCRIPTION cntl 23-16 output data control bits |  |

| 15-8                | 485 data [IO31-24]                              |  |

FIGURE 3-3

IP-PARALLEL-3 CONTROL REGISTER 1 BIT MAP

## CNTL2-3

\$04 Parallel Control Register Port read/write

|          | CONTROL REGISTER 2             |  |

|----------|--------------------------------|--|

| DATA BIT | DESCRIPTION                    |  |

| 3-0      | 485 data [IO35-32]             |  |

| 15-4     | 485 direction 1 = TX [IO35-24] |  |

|          |                                |  |

FIGURE 4-3

IP-PARALLEL-3 CONTROL REGISTER 2 BIT MAP

- 1. All bits are active low and are reset on power-up. Default to 'FFFF', off state for TTL mode and default to inputs in 485 mode.

- 2. In TTL mode each CNTL bit directly corresponds to an IO bit.

- 3. In mixed and 485 modes the cntl bits are re-mapped to push the 485 definitions to the upper bits, and to separate data and direction.

\$00 Parallel Control Register Port read/write

| CONTROL | REGISTER 0 |

|---------|------------|

|---------|------------|

DATA BIT DESCRIPTION

15-0 cntl 15-0 output data control bits

FIGURE 2-4

IP-PARALLEL-4 CONTROL REGISTER 0 BIT MAP

#### CNTL1-4

\$02 Parallel Control Register Port read/write

| CO | NTROL | REGISTER 1 |  |

|----|-------|------------|--|

|    |       |            |  |

**DATA BIT**15-0 **DESCRIPTION**485 data [IO31-16]

FIGURE 3-4

IP-PARALLEL-4 CONTROL REGISTER 1 BIT MAP

## CNTL2-4

\$04 Parallel Control Register Port read/write

## **CONTROL REGISTER 2**

DATA BIT DESCRIPTION

15-0 485 direction 1 = TX [IO31-16]

FIGURE 4-4

IP-PARALLEL-4 CONTROL REGISTER 2 BIT MAP

- 1. All bits are active low and are reset on power-up. Default to 'FFFF', off state for TTL mode and default to inputs in 485 mode.

- 2. In TTL mode each CNTL bit directly corresponds to an IO bit.

- 3. In mixed and 485 modes the cntl bits are re-mapped to push the 485 definitions to the upper bits, and to separate data and direction.

\$00 Parallel Control Register Port read/write

|                                | CONTROL REGISTER 0                                                     |  |

|--------------------------------|------------------------------------------------------------------------|--|

| <b>DATA BIT</b><br>7-0<br>15-8 | <b>DESCRIPTION</b> cntl 7-0 output data control bits 485 data [IO15-8] |  |

FIGURE 2-5

IP-PARALLEL-5 CONTROL REGISTER 0 BIT MAP

## CNTL1-5

\$02 Parallel Control Register Port read/write

| DATA BIT | DESCRIPTION                   |                         |

|----------|-------------------------------|-------------------------|

| 11-0     | 485 data [IO27-16]            |                         |

| 15-12    | 485 direction 1 = TX [IO11-8] |                         |

|          | 11-0                          | 11-0 485 data [IO27-16] |

FIGURE 3-5

IP-PARALLEL-5 CONTROL REGISTER 1 BIT MAP

## CNTL2-5

\$04 Parallel Control Register Port read/write

|                         | CONTROL REGISTER 2                                |  |

|-------------------------|---------------------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> 485 direction 1 = TX [IO27-12] |  |

FIGURE 4-5

IP-PARALLEL-5 CONTROL REGISTER 2 BIT MAP

- 1. All bits are active low and are reset on power-up. Default to 'FFFF', off state for TTL mode and default to inputs in 485 mode.

- 2. In TTL mode each CNTL bit directly corresponds to an IO bit.

- 3. In mixed and 485 modes the cntl bits are re-mapped to push the 485 definitions to the upper bits, and to separate data and direction.

\$00 Parallel Control Register Port read/write

|                         | CONTROL REGISTER 0                   |  |

|-------------------------|--------------------------------------|--|

| <b>DATA BIT</b><br>15-0 | <b>DESCRIPTION</b> 485 data [IO15-0] |  |

**FIGURE 2-485**

IP-PARALLEL-485 CONTROL REGISTER 0 BIT MAP

## CNTL1-485

\$02 Parallel Control Register Port read/write

| IT DESCI | RIPTION       |                       |  |

|----------|---------------|-----------------------|--|

|          | 111111111     |                       |  |

| 485 da   | ata [IO23-16] |                       |  |

|          |               |                       |  |

|          |               | 485 Direction [IO7-0] |  |

**FIGURE 3-485**

IP-PARALLEL-485 CONTROL REGISTER 1 BIT MAP

#### CNTL2-485

\$04 Parallel Control Register Port read/write

| CONTROL REGISTER 2    |                                    |  |

|-----------------------|------------------------------------|--|

| <b>DATA E</b><br>15-0 | DESCRIPTION 485 direction [IO23-8] |  |

**FIGURE 4-485**

IP-PARALLEL-485 CONTROL REGISTER 2 BIT MAP

- 1. All bits are active low and are reset on power-up. Default to 'FFFF', off state for TTL mode and default to inputs in 485 mode.

- 2. In TTL mode each CNTL bit directly corresponds to an IO bit.

- 3. In mixed and 485 modes the cntl bits are re-mapped to push the 485 definitions to the upper bits, and to separate data and direction.

## **Bit Mapping Tables**

| " <b>TT</b> ! !! /40 TT! !! )       |                               |

|-------------------------------------|-------------------------------|

| "-TTL" (48 TTL lines)               |                               |

| <u>IO</u>                           | CNTL (#/Definition)           |

| 47-0                                | 47-0/TTL level IO [IO47-0]    |

|                                     |                               |

| " <b>-1</b> " (40 TTL and 4 – '485) |                               |

| IO `                                | CNTL (#/Definition)           |

| 47-44,23-20                         | 47-44/485 direction control   |

| ,                                   | 43-40/485 data bits [IO43-40] |

| 43-24,19-0                          | 39-0/TTL Level IO [IO39-0]    |

| 40 24, 10 0                         |                               |

| <b>"-2"</b> (32 TTL and 8 – '485)   |                               |

| _ `                                 | CNTI (#/Definition)           |

| <u>IO</u>                           | CNTL (#/Definition)           |

| 47-40,23-16                         | 47-40/485 direction control   |

| 00.04.45.0                          | 39-32/485 data bits [IO39-32] |

| 39-24,15-0                          | 31-0/TTL Level IO [IO31-0]    |

|                                     |                               |

| "-3" (24 TTL and 12 – '485)         |                               |

| <u>IO</u>                           | CNTL (#/Definition)           |

| 47-36,23-12                         | 47-36/485 direction control   |

|                                     | 35-24/485 data bits [IO35-24] |

| 35-24,11-0                          | 23-0/TTL Level IO [IO23-0]    |

|                                     |                               |

| " <b>-4"</b> (16 TTL and 16 – '485) |                               |

| IO                                  | CNTL (#/Definition)           |

| 47-32,23-8                          | 47-32/485 direction control   |

| 62,26 6                             | 31-16/485 data bits [IO31-16] |

| 31-24,7-0                           | 15-0/TTL Level IO [IO15-0]    |

| 31 24,7 0                           |                               |

| " <b>-5"</b> (8 TTL and 20 – '485)  |                               |

| IO                                  | CNTL (#/Definition)           |

| 47-28,23-4                          | 47-28/485 direction control   |

| 47-20,23-4                          |                               |

| 27.24.2.0                           | 27-8/485 data bits [IO27-8]   |

| 27-24,3-0                           | 7-0/TTL Level IO [IO7-0]      |

| " <b>405</b> " (04 (405)            |                               |

| " <b>-485</b> " (24 – '485)         | ONTI (IIID - C - '' )         |

| IO .                                | CNTL (#/Definition)           |

| 47-0                                | 47-24/485 direction control   |

|                                     | 23-0/485 data bits [IO23-0]   |

Please note: (1) IO numbers above are re-arranged to put TTL together and 485

together. Actual IO numbers on the schematic are different. (2) differential pairs are composed of adjacent IO pairs. For example: IO47 IO46 are a pair; when in the –1 through –485 mode. Please refer to the IO tables for complete pin assignments.

Base\_CNTL

\$06 BISERIAL Control Register Port read/write

| CONTROL REGISTER BASE |                                      |  |

|-----------------------|--------------------------------------|--|

| DATA BIT              | DESCRIPTION                          |  |

| 15                    | spare                                |  |

| 14                    | hold timerB 0 = disabled, 1 = hold   |  |

| 13                    | clear timerB 0 = run, 1 = clear      |  |

| 12                    | interrupt enable timerB 1 = enabled  |  |

| 11                    | spare                                |  |

| 10                    | square wave output 1 = output on msb |  |

| 9                     | timerA load 0 = run , 1 = load       |  |

| 8                     | interrupt enable timerA 1 = enabled  |  |

| 7-3                   | spare                                |  |

| 2                     | force interrupt 1 = force            |  |

| 1                     | master interrupt enable 1 = enabled  |  |

| 0                     | output register control 1 = enabled  |  |

|                       |                                      |  |

#### FIGURE 5

#### IP-PARALLEL-IO BASE CONTROL REGISTER BIT MAP

- 1. Output Register Control is used to control when the three Control registers values are placed onto the output registers. If synchronization is needed set to '0' until the registers are written and then enable ['1']. The output bits will then be driven to the new state at the same time. Referenced to the IP Clock. If the bit is left in the '0' state, then the new control register values will not be output and the data will stay in the previous state. If the bit is left in the '1' state the control outputs will change when the registers are independently updated.

- 2. INT\_EN is the master interrupt enable. Default is 0. If set to 1 then if one or more of the filtered input data or timer interrupt conditions is met an interrupt will be generated on level 0.

- 3. Force Interrupt is used to create an interrupt for test and software development purposes. Set the bit to cause an interrupt and clear the bit to remove the interrupt. The IO bits can be used for the same purpose if the filter controls are properly set. Requires INT EN to be enabled.

- 4. Interrupt Enable TimerA. When enabled and the Counter/Timer A is active the counter timer will create an interrupt stream. The period of the interrupts is determined by the pre-load register. The interrupt is generated when the Counter/Timer A counts down to "0". Requires INT\_EN to be enabled.

- 5. Counter/Timer A load when '1' loads the value in the preload register into the down counter. When '0' the counter decrements until the terminal count of "0" is reached at which point the counter re-loads the pre-load value and repeats the cycle. The load bit is not needed because the counter will eventually roll over and reload anyway. If a large count was previously loaded or if the software wants to have a consistent period from a known point in time then the load bit should be used.

- 6. WaveOut when enabled selects the waveform generated by Counter/Timer A to output on the MSBit instead of the data bit for that position. 1 = waveform, 0 = databit. The waveform is a square wave which is switched at each zero crossing has 2x period of the interrupts generated by Counter/Timer A.

- 7. Interrupt Enable Counter/Timer B when '1' creates an interrupt stream based on the second counter timer. Counter/Timer B is a 32 bit up counter. The counter output is masked with the value in the mask register to pick off the period you desire for the interrupt stream. For example: with the IP clock set to 8 Mhz and the mask set to a 0x00000040 the7th bit would be selected for a divide by 64\*2\*125 = 16 uS period. Requires INT\_EN to be enabled to cause an interrupt.

- 8. Clear Counter/Timer B when '1' forces the second counter timer to 0. This function is useful to restart the "real time clock" to a known value at a known time.

- 9. Hold Timer when '1' will stop the Counter/Timer B from updating the read-back register. Counter/Timer B will continue to run. The register will be stable allowing the two reads of the register data to happen without the stored count changing. "0" = update the counter read-back register.

## **INTerrupt Enable**

## Int\_en0 \$08 Parallel Control Register Port read/write

| Interrupt Enable |                                                           |  |

|------------------|-----------------------------------------------------------|--|

| DATA BIT         | DESCRIPTION                                               |  |

| 15-0             | int_en 15-0<br>Interrupt Enable 1 = enabled, 0 = disabled |  |

FIGURE 6

IP-PARALLEL-IO INTERRUPT ENABLE 0 BIT MAP

## Int en1 \$0A Parallel Control Register Port read/write

| Interrupt Enable |                                                            |  |

|------------------|------------------------------------------------------------|--|

| DATA BIT         | DESCRIPTION                                                |  |

| 15-0             | int_en 31-16<br>Interrupt Enable 1 = enabled, 0 = disabled |  |

FIGURE 7

IP-PARALLEL-IO INTERRUPT ENABLE 1 BIT MAP

## Int en2 \$0C Parallel Control Register Port read/write

| Interrupt Enable |                                                            |  |

|------------------|------------------------------------------------------------|--|

| DATA BIT         | DESCRIPTION                                                |  |

| 15-0             | int_en 47-32<br>Interrupt Enable 1 = enabled, 0 = disabled |  |

FIGURE 8

IP-PARALLEL-IO INTERRUPT ENABLE 2 BIT MAP

The data bits correspond to the IO lines. In the filtered path if the control register bit is set to 1 then the corresponding IO line is enabled to be a potential interrupter and to be captured by the hold circuit. The enable is applied after the inversion control. In 485 mode the bits corresponding to the direction control should be set to '0'.

## INTerrupt Edge\_LvI

## Edg Lvl 0 \$10 Parallel Control Register Port read/write

| EDGE_LVL |                                      |

|----------|--------------------------------------|

| DATA BIT | DESCRIPTION                          |

| 15-0     | Edge_Lvl 15-0<br>1 = edge, 0 = level |

FIGURE 9

IP-PARALLEL-IO INTERRUPT EDG\_LVL 0 BIT MAP

## Edg Lvl 1 \$12 Parallel Control Register Port read/write

| EDGE_LVL |                                       |

|----------|---------------------------------------|

| DATA BIT | DESCRIPTION                           |

| 15-0     | Edge_Lvl 31-16<br>1 = edge, 0 = level |

FIGURE 10

IP-PARALLEL-IO INTERRUPT EDG\_LVL 1 BIT MAP

## Edg Lvl 2 \$14 Parallel Control Register Port read/write

| EDGE_LVL |                                       |  |

|----------|---------------------------------------|--|

| DATA BIT | DESCRIPTION                           |  |

| 15-0     | Edge_Lvl 47-32<br>1 = edge, 0 = level |  |

FIGURE 11

IP-PARALLEL-IO INTERRUPT EDG LVL 2 BIT MAP

The data bits correspond to the IO lines. In the filtered path if the control register bit is set to 1 then the corresponding IO line is captured only if there is a transition from '0' to '1'. If set to '0' then anytime the IO line is detected to be '1' the hold circuit will be set. The hold circuit will retain the data until read by the corresponding data\_in\_fi(x) is accessed. The hold circuits are after the enable and inversion in the pipeline. In 485 mode the bits corresponding to the direction control should be set to '0'.

## **INTerrupt Polarity**

## Pol 0 \$18 Parallel Control Register Port read/write

| Polarity |                                          |

|----------|------------------------------------------|

| DATA BIT | DESCRIPTION                              |

| 15-0     | POL 15-0<br>1 = invert, 0 = not inverted |

FIGURE 12

IP-PARALLEL-IO INTERRUPT POL 0 BIT MAP

## Pol 1 \$1A Parallel Control Register Port read/write

| Polarity |                                           |

|----------|-------------------------------------------|

| DATA BIT | DESCRIPTION                               |

| 15-0     | POL 31-16<br>1 = invert, 0 = not inverted |

FIGURE 13

IP-PARALLEL-IO INTERRUPT POL 1 BIT MAP

## Pol 2 \$1C Parallel Control Register Port read/write

| Polarity |                                           |  |

|----------|-------------------------------------------|--|

| DATA BIT | DESCRIPTION                               |  |

| 15-0     | POL 47-32<br>1 = invert, 0 = not inverted |  |

FIGURE 14

IP-PARALLEL-IO INTERRUPT POL 2 BIT MAP

The data bits correspond to the IO lines. In the filtered path if the control register bit is set to 1 then the corresponding IO line is inverted. If set to '0' then no inversion is applied. In 485 mode the bits corresponding to the direction control should be set to '0'.

## **Data Input Filtered**

## Datain fil0 \$20 Parallel Control Register Port read/write

| Filtered Data |                 |  |

|---------------|-----------------|--|

| DATA BIT      | DESCRIPTION     |  |

| 15-0          | DATAIN_FIL 15-0 |  |

FIGURE 15

IP-PARALLEL-IO INTERRUPT DATAIN\_FIL0 BIT MAP

## Datain fil1 \$22 Parallel Control Register Port read/write

| Filtered Data |                  |  |

|---------------|------------------|--|

| DATA BIT      | DESCRIPTION      |  |

| 15-0          | DATAIN_FIL 31-16 |  |

FIGURE 16

IP-PARALLEL-IO INTERRUPT DATAIN\_FIL1 BIT MAP

## Datain fil2 \$24 Parallel Control Register Port read/write

| Filtered Data |                  |  |

|---------------|------------------|--|

| DATA BIT      | DESCRIPTION      |  |

| 15-0          | DATAIN_FIL 47-32 |  |

FIGURE 17

IP-PARALLEL-IO INTERRUPT DATAIN\_FIL2 BIT MAP

The data bits correspond to the IO lines after the filters have been applied. The data remains latched until the register is read. The three registers are independent for reading and clearing purposes. In 485 mode, the bits corresponding to the control are forced to '0'. Read [clear] the registers after any control change to insure that no false positives are reported

## **Data Input Direct**

## Datain dir0 \$28 Parallel Control Register Port read/write

| Direct Data |                 |  |

|-------------|-----------------|--|

| DATA BIT    | DESCRIPTION     |  |

| 15-0        | DATAIN_DIR 15-0 |  |

FIGURE 18

IP-PARALLEL-IO INTERRUPT DATAIN\_DIR0 BIT MAP

## Datain dir1 \$2A Parallel Control Register Port read/write

| Direct Data |                  |  |

|-------------|------------------|--|

| DATA BIT    | DESCRIPTION      |  |

| 15-0        | DATAIN_DIR 31-16 |  |

FIGURE 19

IP-PARALLEL-IO INTERRUPT DATAIN\_DIR1 BIT MAP

## Datain dir2 \$2C Parallel Control Register Port read/write

| Direct Data |                  |  |

|-------------|------------------|--|

| DATA BIT    | DESCRIPTION      |  |

| 15-0        | DATAIN_DIR 47-32 |  |

FIGURE 20

IP-PARALLEL-IO INTERRUPT DATAIN\_DIR2 BIT MAP

The data bits correspond to the IO lines without filters being applied. The data is a direct reflection of the current state of the IO lines. Metastable protection registers are in place but no hold registers. In 485 mode, the bits corresponding to the control are forced to '0'.

## **Pre-Load Registers**

## pre load I \$2E Parallel Control Register Port read/write

| Counter Preload Data |               |  |

|----------------------|---------------|--|

| DATA BIT             | DESCRIPTION   |  |

| 15-0                 | pre-load 15-0 |  |

FIGURE 21

IP-PARALLEL-IO PRE-LOAD LOWER BIT MAP

## Pre\_load\_u \$30 Parallel Control Register Port read/write

| Counter Preload Data |         |                |

|----------------------|---------|----------------|

| DATA                 | A BIT I | DESCRIPTION    |

| 15-0                 | ) ,     | ore_load 31-16 |

FIGURE 22

IP-PARALLEL-IO PRE-LOAD UPPER BIT MAP

The pre-load registers are combined internally to form a 32 bit pre-load value to use with Counter/Timer A. Counter/Timer A is loaded with the value in the Pre-Load registers when the counter reaches zero. The counter can also be loaded with the software command via the Base register. The counter will count from the value down to zero creating an N+1 total count. The counter will re-load the value on the next count.

The Counter Timer A has the option of creating an interrupt at each zero crossing – period N+1. The wave out option can also be enabled. The waveform is generated by switching each time the zero count is detected. A square wave is generated with a period of 2(N+1). The reference period is the IP clock, 125 nS or 31.25 nS depending on the carrier selection made.

Because of the architecture the period selected with Counter/Timer A is arbitrary. Most OS/CPU cannot handle interrupts faster than 10 uS. The counter output is registered and then checked against a count of 2 and re-registered. The count value checked is '2' to account for the double pipeline delay. The counter will be at "0" when the check reaches "2". Because of the checking scheme the minimum count needs to be larger than '2' or the hardware will miss the first "2" and not see it until the counter rolls over. At 8 MHz. The roll over time is approximately 9 minutes.

FIGURE 23

IP-PARALLEL-IO COUNTER/TIMER A

## **Mask Registers**

mask\_I \$32 Parallel Control Register Port read/write

| Mask Data |             |  |

|-----------|-------------|--|

| DATA BIT  | DESCRIPTION |  |

| 15-0      | mask 15-0   |  |

FIGURE 24

IP-PARALLEL-IO MASK LOWER BIT MAP

mask u \$34 Parallel Control Register Port read/write

| Mask Data |             |  |

|-----------|-------------|--|

| DATA BIT  | DESCRIPTION |  |

| 15-0      | mask 31-16  |  |

FIGURE 25

IP-PARALLEL-IO MASK UPPER BIT MAP

The mask registers are combined internally to form a 32 bit mask value to use with Counter/Timer B. Counter/Timer B is a 32 bit up counter which can be cleared to '0'. The counter rolls over at the maximum count. Each counter bit is masked with the mask registers corresponding position. If the Mask(n) = '1' and the counter(n) is also a '1' then the output will be '1'. The output from the AND array is or'd to determine if any

of the counter bit – mask combinations are active. When a counter bit becomes active and the mask is set an interrupt is generated. The interrupt will be generated on the period of the counter selected with the mask. The counter uses the IP clock as a reference. The period selected is 2 \* 2(n) \* [125 or 31.25]. For example a 0x40 and 8 MHz reference rate would create a periodic interrupt with a period of 16 uS. [2\*64\*125 nS]

## **Read-Back Registers**

## rdbk\_I \$36 Parallel Control Register Port read/write

| Count Data |                |  |

|------------|----------------|--|

| DATA BIT   | DESCRIPTION    |  |

| 15-0       | read-back 15-0 |  |

FIGURE 26

IP-PARALLEL-IO READ-BACK LOWER BIT MAP

## rdbk u \$38 Parallel Control Register Port read/write

| Count Data |                 |  |  |  |  |  |

|------------|-----------------|--|--|--|--|--|

| DATA BIT   | DESCRIPTION     |  |  |  |  |  |

| 15-0       | read-back 31-16 |  |  |  |  |  |

FIGURE 27

IP-PARALLEL-IO READ-BACK UPPER BIT MAP

Counter/TimerB has a read-back port which allows the count to be read by the host. The count is pipelined and stored into an output register. The register is updated with each count unless the Hold [see base register] bit is set. When the Hold bit is set the output register is disabled from updating; Counter/TimerB continues to count. The register is 32 bits wide. Two reads are required to get the entire 32 bit word via the 16 bit IP data bus. If only the lower or upper words are of interest then the Hold bit can be ignored.

## **Status Register**

## status \$1E Parallel Status read/write

| DESCRIPTION                         |

|-------------------------------------|

|                                     |

| spare read-only                     |

| INTR0 1= interrupt condition active |

| spare                               |

| INTR DAT 1 = active IO Bit          |

| INTRB 1 = active Counter/TimerB     |

| INTRA 1 = active Counter/TimerA     |

|                                     |

FIGURE 29

IP-PARALLEL-IO STATUS BIT MAP

When the interrupt status is set ['1'] then the interrupt event has occurred. If the Interrupt Enable corresponding to the interrupt type and master interrupt enable are set then an interrupt will occur. If the Enable is not set then the interrupt will not be asserted and the status can be used to poll. The Counter/Timer Interrupts are cleared by writing to the status register with the corresponding bit(s) set. Writing to 15-2 will have no affect. The write is transitory – no clear or re-enable is required. The data interrupt is cleared by reading the data from the filtered data ports.

INTR0 is the state of the interrupt condition before the master enable. This bit is useful if operating in a polled mode.

## BIS\_VECTOR

\$0E Parallel Interrupt Vector Port

The Interrupt vector for the IP-Parallel-IO is stored in this byte wide register. This read/write register is initialized to 'xxFF' upon power-on reset. The vector is stored in the odd byte location [D7..0]. The vector should be initialized before the interrupt is enabled or the mask is lowered. The interrupt is automatically cleared when the CPU acknowledges the interrupt.

## Interrupts

All IP Module interrupts are vectored. The vector from the IP-PARALLEL-IO comes from a vector register loaded as part of the initialization process. The vector register can be programmed to any 8 bit value. The default value is \$FF which is sometimes not a valid user vector. The software is responsible for choosing a valid user vector.

The IP-PARALLEL-IO state machines generate an interrupt request when a programmed condition is detected on the IO lines. The interrupt is mapped to interrupt request 0. The CPU will respond by asserting INT. The hardware will automatically supply the appropriate interrupt vector when accessed by the CPU. The source of the interrupt is obtained by reading DATA\_IN\_FIL0-2. The status remains valid until the registers are read. The interrupt status is auto-cleared when the registers are accessed. The interrupt type can be read from the Status register. There are three interrupt types; Data IO, Counter/Timer A and Counter/Timer B. If both data and timer interrupts are in use then the status register should be read first to determine which interrupt types are active. The exception handler can then respond to all of the current interrupt requests.

Some carrier boards pre-fetch data. If your carrier board pre-fetches the interrupt status, then the status may be cleared when the SW goes to look at it. If this is an issue then be careful with the order of reading the registers to prevent the pre-fetching function from affecting operation.

The interrupt level seen by the CPU is determined by the IP Carrier board being used. The master interrupt can be disabled or enabled through the BASE\_CNTL register. The individual enables for IO lines are controllable through INT\_EN0-2. The enable operates before the interrupt holding latch, which stores the request for the CPU. Once the interrupt request is set, the way to clear the request is to read the holding register [DATAIN\_FIL0-2], reset the board, or disable the interrupt. The Interrupt acknowledge cycle fetches the vector, but does not clear the interrupt request in this design.

If operating in a polled mode and making use of the interrupts for status then the master interrupt should be disabled.

## **ID PROM**

Every IP contains an ID PROM, whose size is at least 32 x 8 bits. The ID PROM aids in software auto configuration and configuration management. The user's software, or a supplied driver, may verify that the device it expects is actually installed at the location it expects, and is nominally functional. The ID PROM contains the manufacturing revision level of the IP. If a driver requires that a particular revision to be present, it may check for it directly.

The location of the ID PROM in the host's address space is dependent on which carrier is used.

Standard data in the ID PROM on the IP-PARALLEL-IO is shown in the figure below. For more information on IP ID PROMs refer to the IP Module Logic Interface Specification, available from Dynamic Engineering.

Each of the modifications to the IP-Parallel-IO board will be recorded with a new code in the DRIVER ID and reserved fields.

| Address | Data                   | TTL  | -1   | -2   | -3   | -4   | -5   | 485  |

|---------|------------------------|------|------|------|------|------|------|------|

| 01      | ASCII "I"              | \$49 | \$49 | \$49 | \$49 | \$49 | \$49 | \$49 |

| 03      | ASCII "P"              | \$50 | \$50 | \$50 | \$50 | \$50 | \$50 | \$50 |

| 05      | ASCII "A"              | \$41 | \$41 | \$41 | \$41 | \$41 | \$41 | \$41 |

| 07      | ASCII "H"              | \$48 | \$48 | \$48 | \$48 | \$48 | \$48 | \$48 |

| 09      | Manufacturer ID        | \$1E |

| 0B      | Model Number           | \$03 | \$03 | \$03 | \$03 | \$03 | \$03 | \$03 |

| 0D      | Revision               | \$A0 |

| 0F      | reserved               | \$00 | \$00 | \$00 | \$00 | \$00 | \$00 | \$00 |

| 11      | Driver ID, low byte    | \$00 | \$00 | \$00 | \$00 | \$00 | \$00 | \$00 |

| 13      | Driver ID, high byte   | \$00 | \$01 | \$02 | \$03 | \$04 | \$05 | \$06 |

| 15      | No of extra bytes used | \$0C |

| 17      | CRC                    | \$68 | \$58 | \$08 | \$38 | \$A8 | \$98 | \$C8 |

|         |                        |      |      |      |      |      |      |      |

FIGURE 30 IP-PARALLEL-IO ID PROM

## **IP-Parallel-x Logic Interface Pin Assignment**

The figure below gives the pin assignments for the IP Module Logic Interface on the IP-PARALLEL-IO. Pins marked n/c below are defined by the specification, but not used on the IP-PARALLEL-IO. Also see the User Manual for your carrier board for more information.

| GND    |      | GND     |         | 1  |     | 26 |     |

|--------|------|---------|---------|----|-----|----|-----|

|        | CLK  |         | +5V     |    | 2   |    | 27  |

| Reset* |      | R/W*    |         | 3  |     | 28 |     |

|        | D0   |         | IDSEL*  |    | 4   |    | 29  |

| D1     |      | DMARed  |         | 5  |     | 30 |     |

|        | D2   |         | MEMSEL* |    | 6   |    | 31  |

| D3     |      | DMARed  |         | 7  | _   | 32 |     |

|        | D4   |         | IntSel* | _  | 8   |    | 33  |

| D5     | 5.0  | DMAck*  |         | 9  | 4.0 | 34 | 0=  |

|        | D6   |         | IOSel*  |    | 10  |    | 35  |

| D7     | D0   | n/c     | A.4     | 11 | 40  | 36 | 0.7 |

| DO     | D8   |         | A1      | 40 | 12  | 20 | 37  |

| D9     | D10  | DMAEnd  |         | 13 | 14  | 38 | 39  |

| D11    | טוט  | n/c     | A2      | 15 | 14  | 40 | 39  |

| ווט    | D12  |         | A3      | 15 | 16  | 40 | 41  |

| D13    | D12  | IntReq0 |         | 17 | 10  | 42 | 71  |

| D.10   | D14  | ma toqo | A4      | ., | 18  |    | 43  |

| D15    | 511  | IntReq1 |         | 19 | .0  | 44 | .0  |

|        | BS0* |         | A5      |    | 20  |    | 45  |

| BS1*   |      | n/c     |         | 21 |     | 46 |     |

|        | n/c  |         | A6      |    | 22  |    | 47  |

| n/c    |      | Ack*    |         | 23 |     | 48 |     |

|        | +5V  |         | n/c     |    | 24  |    | 49  |

| GND    |      | GND     |         | 25 |     | 50 |     |

| GND    |      | GND     |         | 25 |     | 50 |     |

NOTE 1: The no-connect signals above are defined by the IP Module Logic Interface Specification, but not used by this IP. See the Specification for more information.

NOTE 2: The layout of the pin numbers in this table corresponds to the physical placement of pins on the IP connector. Thus this table may be used to easily locate the physical pin corresponding to a desired signal. Pin 1 is marked with a square pad on the IP Module.

FIGURE 31

IP-PARALLEL-IO LOGIC INTERFACE

# **IP-Parallel-IO Interface Pin Assignment**

The figure below gives the pin assignments for the IP Module IO Interface on the IP-PARALLEL-IO. Pins marked. Also see the User Manual for your carrier board for more information.

| IO_0                     | IO_24 |        | 1  |    | 26 |     |  |

|--------------------------|-------|--------|----|----|----|-----|--|

| 10 4                     |       | IO_25  |    | 2  |    | 27  |  |

| 10_1<br>10_2<br>10_3     | IO_26 | 10. 07 | 3  | 4  | 28 | 20  |  |

| 10_3<br>10_4             | IO_28 | IO_27  | 5  | 4  | 30 | 29  |  |

| IO_ <del>-</del><br>IO 5 | 10_20 | IO_29  | 3  | 6  | 30 | 31  |  |

| IO_4<br>IO_5<br>IO_6     | IO_30 |        | 7  | ·  | 32 | •   |  |

| 1/1 7                    |       | IO_31  |    | 8  |    | 33  |  |

| IO_7<br>IO_8<br>IO_9     | IO_32 | 10.00  | 9  | 40 | 34 | 0.5 |  |

| 10_9<br>10_10            | IO_34 | IO_33  | 11 | 10 | 36 | 35  |  |

| IO_10<br>IO_11           | 10_04 | IO_35  | 11 | 12 | 50 | 37  |  |

| IO_12                    | IO_36 |        | 13 |    | 38 |     |  |

| IO 13                    |       | IO_37  |    | 14 |    | 39  |  |

| IO_14                    | IO_38 | 10.00  | 15 | 40 | 40 | 4.4 |  |

| IO_15<br>IO_16           | IO_40 | IO_39  | 17 | 16 | 42 | 41  |  |

| IO_10<br>IO_17           | 10_40 | IO_41  | 17 | 18 | 72 | 43  |  |

| IO_18                    | IO_42 |        | 19 |    | 44 |     |  |

| IO 19                    |       | IO_43  |    | 20 |    | 45  |  |

| IO_20                    | IO_44 | 10.45  | 21 | 22 | 46 | 47  |  |

| IO_21                    | IO_46 | IO_45  | 23 | 22 | 48 | 47  |  |

| IO_22<br>IO_23           | 10_+0 | IO_47  | 23 | 24 | +0 | 49  |  |

| GND                      | GND   |        | 25 |    | 50 |     |  |

|                          |       |        |    |    |    |     |  |

NOTE 1: The layout of the pin numbers in this table corresponds to the physical placement of pins on the IP connector. Thus this table may be used to easily locate the physical pin corresponding to a desired signal. Pin 1 is marked with a square pad on the IP Module. Unused pins should not be connected.

FIGURE 32

IP-PARALLEL-IO IO INTERFACE

# **IP-Parallel-1 Interface Pin Assignment**

The figure below gives the pin assignments for the IP Module IO Interface on the IP-PARALLEL-1. Pins marked. Also see the User Manual for your carrier board for more information.

| IO_0                         | IO_20  | 10.04  | 1  |    | 26 | 0=  |

|------------------------------|--------|--------|----|----|----|-----|

| IO_1<br>IO_2<br>IO_3<br>IO 4 | 10 22  | IO_21  | 3  | 2  | 28 | 27  |

| 10_2                         | IO_22  | IO_23  | 3  | 4  | 20 | 29  |

| IO 4                         | IO_24  | 10_23  | 5  | 7  | 30 | 25  |

| IO_4<br>IO_5                 |        | IO_25  | ·  | 6  |    | 31  |

| IO_6                         | IO_26  | _      | 7  |    | 32 |     |

| IO_7<br>IO_8                 |        | IO_27  |    | 8  |    | 33  |

| IO_8                         | IO_28  | 10.00  | 9  | 40 | 34 | 0.5 |

| IO_9<br>IO_10                | IO 30  | IO_29  | 11 | 10 | 36 | 35  |

| IO_10<br>IO_11               | IO_30  | IO_31  | 11 | 12 | 30 | 37  |

| IO_12                        | IO_32  | 10_01  | 13 | 12 | 38 | 01  |

| IO_13                        |        | IO_33  |    | 14 |    | 39  |

| IO_14                        | IO_34  | _      | 15 |    | 40 |     |

| IO_15                        |        | IO_35  |    | 16 |    | 41  |

| IO_16                        | IO_36  | 10.07  | 17 | 40 | 42 | 40  |

| IO_17<br>IO_18               | IO_38  | IO_37  | 19 | 18 | 44 | 43  |

| IO_18<br>IO_19               | 10_36  | IO_39  | 19 | 20 | 44 | 45  |

| IO_40+                       | IO_42+ | .0_00  | 21 | 20 | 46 |     |

| IO_40-                       | _      | IO_42- |    | 22 |    | 47  |

| IO_41-                       | IO_43- |        | 23 |    | 48 |     |

| IO_41+                       | a      | IO_43+ |    | 24 |    | 49  |

| GND                          | GND    |        | 25 |    | 50 |     |

|                              |        |        |    |    |    |     |

NOTE 1: The layout of the pin numbers in this table corresponds to the physical placement of pins on the IP connector. Thus this table may be used to easily locate the physical pin corresponding to a desired signal. Pin 1 is marked with a square pad on the IP Module. Unused pins should not be connected.

FIGURE 33

IP-PARALLEL-1 IO INTERFACE

# **IP-Parallel-2 Interface Pin Assignment**

The figure below gives the pin assignments for the IP Module IO Interface on the IP-PARALLEL-2. Pins marked. Also see the User Manual for your carrier board for more information.

| 10.0             | 10.40  |        |    |     |    |            |

|------------------|--------|--------|----|-----|----|------------|

| IO_0<br>IO_1     | IO_16  | IO_17  | 1  | 2   | 26 | 27         |

| IO_2             | IO_18  | 10_11  | 3  | _   | 28 | <b>-</b> : |

| 10_3             |        | IO_19  | _  | 4   |    | 29         |

| IO_4<br>IO_5     | IO_20  | IO_21  | 5  | 6   | 30 | 31         |

| IO_5<br>IO_6     | IO_22  | 10_21  | 7  | U   | 32 | J i        |

| IO 7             |        | IO_23  |    | 8   |    | 33         |

| 10_8             | IO_24  | 10. 25 | 9  | 10  | 34 | 35         |

| IO_9<br>IO_10    | IO_26  | IO_25  | 11 | 10  | 36 | ათ         |

| IO_11            |        | IO_27  |    | 12  |    | 37         |

| IO_12            | IO_28  | 10.00  | 13 | 4.4 | 38 | 00         |

| IO_13<br>IO_14   | IO_30  | IO_29  | 15 | 14  | 40 | 39         |

| IO_15            | .0_00  | IO_31  |    | 16  |    | 41         |

| IO_32+           | IO_36+ |        | 17 | 4.0 | 42 |            |

| IO_32-<br>IO_33- | IO_37- | IO_36- | 19 | 18  | 44 | 43         |

| IO 33+           |        | IO_37+ | 10 | 20  |    | 45         |

| IO_34+           | IO_38+ |        | 21 |     | 46 | 4-         |

| IO_34-<br>IO_35- | IO_39- | IO_38- | 23 | 22  | 48 | 47         |

| IO_35+           | 10_33- | IO_39+ | 23 | 24  | 40 | 49         |

| GND _            | GND    | _      | 25 |     | 50 |            |

|                  |        |        |    |     |    |            |

NOTE 1: The layout of the pin numbers in this table corresponds to the physical placement of pins on the IP connector. Thus this table may be used to easily locate the physical pin corresponding to a desired signal. Pin 1 is marked with a square pad on the IP Module. Unused pins should not be connected.

FIGURE 34

IP-PARALLEL-2 IO INTERFACE

# **IP-Parallel-3 Interface Pin Assignment**

The figure below gives the pin assignments for the IP Module IO Interface on the IP-PARALLEL-3. Pins marked. Also see the User Manual for your carrier board for more information.

| 10.0             | 10.46  |         | 4  |     | 00             |    |

|------------------|--------|---------|----|-----|----------------|----|

| IO_0<br>IO_1     | IO_12  | IO_13   | 1  | 2   | 26             | 27 |

| IO_2             | IO_14  |         | 3  |     | 28             |    |

| 10_3             | IO 16  | IO_15   | 5  | 4   | 30             | 29 |

| IO_4<br>IO_5     | IO_16  | IO_17   | 5  | 6   | 30             | 31 |

| IO_6             | IO_18  |         | 7  |     | 32             |    |

| IO_7<br>IO_8     | IO_20  | IO_19   | 9  | 8   | 34             | 33 |

| IO_0<br>IO_9     | 10_20  | IO_21   | 9  | 10  | J <del>4</del> | 35 |

| IO_10            | IO_22  |         | 11 |     | 36             |    |

| IO_11<br>IO_24+  | IO_30+ | IO_23   | 13 | 12  | 38             | 37 |

| IO 24-           |        | IO_30-  | 10 | 14  | 00             | 39 |

| IO_25-           | IO_31- |         | 15 | 4.0 | 40             |    |

| IO_25+<br>IO_26+ | IO_32+ | IO_31+  | 17 | 16  | 42             | 41 |

| IO_26-           |        | IO_32-  |    | 18  |                | 43 |

| IO_27-           | IO_33- | 10. 221 | 19 | 20  | 44             | 4E |

| IO_27+<br>IO_28+ | IO_34+ | IO_33+  | 21 | 20  | 46             | 45 |

| IO_28-           |        | IO_34-  |    | 22  |                | 47 |

| IO_29-<br>IO_29+ | IO_35- | IO_35+  | 23 | 24  | 48             | 49 |

| 10_29+<br>GND    | GND    | 10_001  | 25 | 4   | 50             | 70 |

|                  |        |         |    |     |                |    |

NOTE 1: The layout of the pin numbers in this table corresponds to the physical placement of pins on the IP connector. Thus this table may be used to easily locate the physical pin corresponding to a desired signal. Pin 1 is marked with a square pad on the IP Module. Unused pins should not be connected.

FIGURE 35

IP-PARALLEL-3 IO INTERFACE

# **IP-Parallel-4 Interface Pin Assignment**

The figure below gives the pin assignments for the IP Module IO Interface on the IP-PARALLEL-4. Pins marked. Also see the User Manual for your carrier board for more information.

| IO_0             | IO_8   |        | 1  |     | 26 |    |  |

|------------------|--------|--------|----|-----|----|----|--|

| IO_1             |        | IO_9   |    | 2   |    | 27 |  |

| IO_2             | IO_10  | 10.44  | 3  |     | 28 | 00 |  |

| 10_3             | IO 12  | IO_11  | 5  | 4   | 30 | 29 |  |

| IO_4<br>IO_5     | IO_12  | IO_13  | 5  | 6   | 30 | 31 |  |

| IO_6             | IO_14  | 10_10  | 7  | Ŭ   | 32 | 01 |  |

| IO_7             |        | IO_15  |    | 8   |    | 33 |  |

| IO_16+           | IO_24+ |        | 9  |     | 34 |    |  |

| IO_16-           | 10. 25 | IO_24- | 44 | 10  | 20 | 35 |  |

| IO_17-<br>IO_17+ | IO_25- | IO_25+ | 11 | 12  | 36 | 37 |  |

| IO_18+           | IO_26+ | 10_231 | 13 | 12  | 38 | 31 |  |

| IO_18-           |        | IO_26- |    | 14  |    | 39 |  |

| IO_19-           | IO_27- | _      | 15 |     | 40 |    |  |

| IO_19+           |        | IO_27+ |    | 16  |    | 41 |  |

| IO_20+           | IO_28+ | 10.00  | 17 | 40  | 42 | 40 |  |

| IO_20-<br>IO_21- | IO_29- | IO_28- | 19 | 18  | 44 | 43 |  |

| IO_21+           | 10_23  | IO_29+ | 10 | 20  | 77 | 45 |  |

| IO_22+           | IO_30+ |        | 21 |     | 46 | -  |  |

| IO_22-           |        | IO_30- |    | 22  |    | 47 |  |

| IO_23-           | IO_31- | 10.04  | 23 | 0.4 | 48 | 40 |  |

| IO_23+<br>GND    | GND    | IO_31+ | 25 | 24  | 50 | 49 |  |

| GIND             | GND    |        | 23 |     | 50 |    |  |

|                  |        |        |    |     |    |    |  |

NOTE 1: The layout of the pin numbers in this table corresponds to the physical placement of pins on the IP connector. Thus this table may be used to easily locate the physical pin corresponding to a desired signal. Pin 1 is marked with a square pad on the IP Module. Unused pins should not be connected.

FIGURE 36

IP-PARALLEL-4 IO INTERFACE

# **IP-Parallel-5 Interface Pin Assignment**

The figure below gives the pin assignments for the IP Module IO Interface on the IP-PARALLEL-5. Pins marked. Also see the User Manual for your carrier board for more information.

| IO_0             | IO_4   |          | 1   |    | 26 |     |

|------------------|--------|----------|-----|----|----|-----|

| IO_1             |        | IO_5     | _   | 2  |    | 27  |

| IO_2             | IO_6   | 10. 7    | 3   | 4  | 28 | 20  |

| IO_3<br>IO_8+    | IO_18+ | 10_7     | 5   | 4  | 30 | 29  |

| IO_8-            | 10_101 | IO_18-   | 3   | 6  | 30 | 31  |

| IO_9-            | IO_19- | 10_10    | 7   | J  | 32 | 01  |

| IO_9+            |        | IO_19+   |     | 8  |    | 33  |

| IO 10+           | IO_20+ |          | 9   |    | 34 |     |

| IO_10-           | 10.04  | IO_20-   |     | 10 |    | 35  |

| IO_11-           | IO_21- | 10. 24 i | 11  | 10 | 36 | 37  |

| IO_11+<br>IO_12+ | IO_22+ | IO_21+   | 13  | 12 | 38 | 31  |

| IO_12-           | 10_221 | IO_22-   | 10  | 14 | 30 | 39  |

| IO_13-           | IO_23- | .0_22    | 15  |    | 40 |     |

| _<br>IO_13+      | _      | IO_23+   |     | 16 |    | 41  |

| IO_14+           | IO_24+ |          | 17  |    | 42 |     |

| IO_14-           |        | IO_24-   | 4.0 | 18 |    | 43  |

| IO_15-           | IO_25- | 10. 25.  | 19  | 20 | 44 | 45  |

| IO_15+<br>IO_16+ | IO_26+ | IO_25+   | 21  | 20 | 46 | 40  |

| IO_16-           | 10_201 | IO_26-   | 21  | 22 | 70 | 47  |

| IO_17-           | IO_27- |          | 23  |    | 48 | • • |

| IO_17+           |        | IO_27+   |     | 24 |    | 49  |

| GND              | GND    |          | 25  |    | 50 |     |

|                  |        |          |     |    |    |     |