DHTML JavaScript Website Pull Down Navigation Menu By Milonic

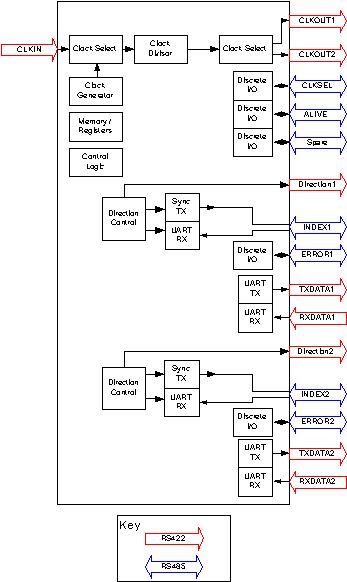

PMC-BiSerial II-NG1 PMC Compatible Bi-Directional Serial Data Interface Please note that the PMC-BiSerial-II has been upgraded and the PMC-BiSerial-III is currently recommended for new designs The PMC BiSerial-II NG1 is part of the PMC Module family of modular I/O components by Dynamic Engineering. The PMC BiSerial-II is capable of providing multiple serial protocols. The NG1 protocol implemented provides two full-duplex RS-422 UART interfaces with error detection, two half-duplex RS-485 custom index interfaces, external clock input, two clock outputs, and various discrete signal inputs and outputs, all using RS-485 transceivers.1 on undriven lines. The terminations and transceivers are programmable through the Xilinx device to provide the proper mix of outputs and inputs and terminations needed for a specific protocol implementation. The PMC BiSerial-II conforms to the PMC and CMC draft standards. This guarantees compatibility with multiple PMC Carrier boards. Because the PMC may be mounted on different form factors, while maintaining plug and software compatibility, system prototyping may be done on one PMC Carrier board, with final system implementation on a different one.standard height and will work in most systems with most carriers. If your carrier has non-standard connectors [height] to mate with the PMC BiSerial-II, please let us know. We may be able to do a special build with a different height connector to compensate.PMC-BiSerial II-NG1 NG1 Block Diagram email us your wish list or call today!

Engineering Kits Related Products: HDEcabl68 SCSI II/III Cable HDEterm68 SCSI II/III to 68 pin terminal block PCI2PMC PCI to PMC adapter card PCIBPMC bridged PCI to PMC adapter card cPCI2PMC cPCI to PMC adapter card 3U 4HP PMC Extendio II PMC extension cable set - move your PMC up to 12" away from the host. You must have Adobe Acrobat to read our PDF files. PMC-BiSerial-II manual PDF PMC-BiSerial-NG1 user manual PDF NG1 Driver manual PDF Custom, IP, PMC, PC*MIP, PCI, VME Hardware, Software designed to your requirements Home |

News |

Search the Dynamic Engineering Site

[an error occurred while processing this directive]