# **DYNAMIC ENGINEERING**

150 DuBois St. Suite C, Santa Cruz, CA 95060 831-457-8891 Fax 831-457-4793 http://www.dyneng.com sales@dyneng.com Est. 1988

# User Manual PMC-BiSerial-III-NG8

Digital Parallel Interface PMC Module Camera Interface Protocols TX & RX 2 Channels RS-485/422

Manual Revision A Corresponding Fab: 10-2005-0204 FLASH 0x0B01

# PMC-BiSerial-III-NG8

Digital Parallel Interface PMC Module Dynamic Engineering 150 DuBois St. Suite C, Santa Cruz CA 95060 831-457-8891 831-457-4793 FAX

This document contains information of proprietary interest to Dynamic Engineering. It has been supplied in confidence and the recipient, by accepting this material, agrees that the subject matter will not be copied or reproduced, in whole or in part, nor its contents revealed in any manner or to any person except to meet the purpose for which it was delivered.

Dynamic Engineering has made every effort to ensure that this manual is accurate and complete. Still, the company reserves the right to make improvements or changes in the product described in this document at any time and without notice. Furthermore, Dynamic Engineering assumes no liability arising out of the application or use of the device described herein.

The electronic equipment described herein generates, uses, and can radiate radio frequency energy. Operation of this equipment in a residential area is likely to cause radio interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Dynamic Engineering's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Dynamic Engineering.

This product has been designed to operate with PMC Module carriers and compatible user-provided equipment. Connection of incompatible hardware is likely to cause serious damage.

©2009 by Dynamic Engineering. Other trademarks and registered trademarks are owned by their respective manufacturers. Revised 11/23/09

# Table of Contents

| PRODUCT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

| ADDRESS MAP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13                                                                                                                   |

| PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 15                                                                                                                   |

| Base Register Definitions<br>NG8_BASE_BASE<br>NG8_BASE_ID<br>NG8_BASE_STATUS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 18<br><b>18</b><br>19<br>20                                                                                          |

| Channel Register Definitions<br>NG8_CHAN_CNTRL<br>NG8_CHAN_STATUS<br>NG8_CHAN_TX_FIFO_COUNT<br>NG8_CHAN_RD_DMA_PNTR<br>NG8_CHAN_RX_FIFO_COUNT<br>NG8_CHAN_RX_FIFO<br>NG8_CHAN_TX_AMT_LVL<br>NG8_CHAN_TX_AMT_LVL<br>NG8_CHAN_TX_CNTRL<br>NG8_CHAN_TX_CNTRL<br>NG8_CHAN_TX_PIXEL_WORD_COUNT<br>NG8_CHAN_TX_FIFO_WORD_COUNT<br>NG8_CHAN_TX_READY_COUNT<br>NG8_CHAN_RX_CNTRL<br>NG8_CHAN_RX_CNTRL<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_FIFO_WORD_COUNT<br>NG8_CHAN_RX_WORD_COUNT<br>NG8_CHAN_RX_WORD_COUNT | 21<br>21<br>24<br>29<br>30<br>30<br>31<br>31<br>32<br>33<br>33<br>34<br>34<br>35<br>36<br>37<br>37<br>38<br>38<br>38 |

| LOOP-BACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 39                                                                                                                   |

| PMC MODULE LOGIC INTERFACE PIN ASSIGNMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40                                                                                                                   |

| PMC MODULE LOGIC INTERFACE PIN ASSIGNMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                                                                                   |

| PMC MODULE REAR IO INTERFACE PIN ASSIGNMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 42                                                                                                                   |

| APPLICATIONS GUIDE           | 43 |

|------------------------------|----|

| Interfacing                  | 43 |

| Construction and Reliability | 44 |

| Thermal Considerations       | 44 |

| Warranty and Repair          | 45 |

| Service Policy               | 45 |

| Out of Warranty Repairs      | 45 |

| SPECIFICATIONS               | 46 |

| ORDER INFORMATION            | 47 |

# List of Figures

| FIGURE 1 PMC-BISERIAL-III-NG8 BLOCK DIAGRAM                     | 9  |

|-----------------------------------------------------------------|----|

| FIGURE 2 PMC-BISERIAL-III-NG8 TIMING DIAGRAM                    | 11 |

| FIGURE 3 IMAGE DIMENSIONS                                       | 11 |

| FIGURE 4 PMC-BISERIAL-III INTERNAL ADDRESS MAP BASE FUNCTIONS   | 13 |

| FIGURE 5 PMC-BISERIAL-III CHANNEL ADDRESS MAP                   | 14 |

| FIGURE 6 PMC-BISERIAL-III CONTROL BASE REGISTER BIT MAP         | 18 |

| FIGURE 7 PMC-BISERIAL-III ID AND SWITCH BIT MAP                 | 19 |

| FIGURE 8 PMC-BISERIAL-III STATUS PORT BIT MAP                   | 20 |

| FIGURE 9 PMC-BISERIAL-III CHANNEL CONTROL REGISTER              | 21 |

| FIGURE 10 PMC-BISERIAL-III CHANNEL STATUS PORT                  | 24 |

| FIGURE 11 PMC-BISERIAL-III WRITE DMA POINTER REGISTER           | 28 |

| FIGURE 12 PMC-BISERIAL-III TRANSMIT DMA FIFO DATA COUNT PORT    | 29 |

| FIGURE 13 PMC-BISERIAL-III READ DMA POINTER REGISTER            | 29 |

| FIGURE 14 PMC-BISERIAL-III RECEIVE DMA FIFO DATA COUNT PORT     | 30 |

| FIGURE 15 PMC-BISERIAL-III RX/TX FIFO PORT                      | 30 |

| FIGURE 16 PMC-BISERIAL-III TRANSMIT ALMOST EMPTY LEVEL REGISTER | 31 |

| FIGURE 17 PMC-BISERIAL-III RECEIVE ALMOST FULL LEVEL REGISTER   | 31 |

| FIGURE 18 PMC-BISERIAL-III CHANNEL TRANSMITTER CONTROL REGISTER | 32 |

| FIGURE 19 PMC-BISERIAL-III TRANSMIT PIXEL COUNT PORT            | 33 |

| FIGURE 20 PMC-BISERIAL-III TARGET DATA COUNT PORT               | 33 |

| FIGURE 21 PMC-BISERIAL-III TX AMT LEVEL CONTROL PORT            | 34 |

| FIGURE 22 PMC-BISERIAL-III TX READY COUNT CONTROL PORT          | 34 |

| FIGURE 23 PMC-BISERIAL-III CHANNEL RECEIVER CONTROL REGISTER    | 35 |

| FIGURE 24 PMC-BISERIAL-III RX PIXELS EXPECTED PORT              | 36 |

| FIGURE 25 PMC-BISERIAL-III RX SM DATA COUNT PORT                | 37 |

| FIGURE 26 PMC-BISERIAL-III RX AFL LEVEL CONTROL PORT            | 37 |

| FIGURE 27 PMC-BISERIAL-III RX AFL LEVEL CONTROL PORT            | 38 |

| FIGURE 28 PMC-BISERIAL-III TX TOTAL FIFO COUNT                  | 38 |

| FIGURE 29 PMC-BISERIAL-III RX TOTAL FIFO COUNT                  | 38 |

| FIGURE 30 PMC-BISERIAL-III PN1 INTERFACE                        | 40 |

| FIGURE 31 PMC-BISERIAL-III PN2 INTERFACE                        | 41 |

| FIGURE 32 PMC-BISERIAL-III REAR PANEL INTERFACE                 | 42 |

# **Product Description**

In embedded systems many of the interconnections are made with differential [RS-422/485 or LVDS] signals. Depending on the system architecture an IP or a PMC will be the right choice to make the connection. You have choices with carriers for cPCI, PCI, VME, PC/104p and other buses for both PMC and IP mezzanine modules.

Usually the choice is based on other system constraints as both the PMC and IP can provide the IO you require. Dynamic Engineering would be happy to assist in your decision regarding architecture and other trade-offs with the PMC / IP decision. Dynamic Engineering has carriers for IP and PMC modules for most systems, and is adding more as new solutions are requested by our clients.

The PMC compatible PMC-BiSerial-III has 34 independent differential IO available. The high density makes efficient use of PMC slot resources. The IO is available for system connection through the front panel [34], via the rear [Pn4] connector [32], or both. A high density 68 pin SCSI III front panel connector provides the front panel IO. The rear panel IO has a PIM and PIM Carrier available for rear panel wiring options.

PMC-BiSerial-III-NG8 is a "clientized" version of the standard PMC-BiSerial-III board. "NG8" is set to use the RS-485 standard, has rear panel IO, and supports two channels each with Transmit or Receive capability. The PLL is programmed with the Transmit reference frequency and the Receive state-machine frequency. The PLL is referenced to 50 MHz. and can be programmed with new .JED files using the driver.

Data is transferred as pixel wide [11-0] with a reference clock, "BadBit", Vertical and Horizontal reference signals. There is no handshaking. The Receiver uses the VREF signal to "know" where the start of an image is. The rising edge of the clock is used to capture the pixel and reference signals. Using the programmable image size count data is captured for a complete image and status set indicating a complete image is ready. The internal memory is able to hold 3 complete images of 288 x 290 and be receiving a 4<sup>th</sup>. DMA is available to insure the data is transferred from the local FIFO to the system.

The transmitter sends data out based on what is stored into memory. The pixels are 12 bits [11-0]. The upper nibble of each word is used to set the clock enable, VREF, HREF, and BadBit signals. The transmitter is designed to force the signals to 0xffff when not actively transmitting.

Software can select between transmit and receive functions for each channel. The direction bit sets the direction for the RS-485 transceivers and the terminations. When in receive mode the terminations are enabled and the transceivers are set to receive.

DMA or single word accesses can be used to load and unload the FIFO's.  $4K \times 32$ FIFO's are used for the DMA transfer TX and RX. In addition there are local Statemachine FIFO's 1Kx32 to handle the rate matching between the bulk storage and the local speed. One external [to the FPGA] 128K x 32 FIFO is assigned to each channel. Buffering around the input and output ports allows the external FIFO to be used for transmit or receive. Total storage for TX is 4K + 1K + 128K. Since each LW holds 2 pixels the memory can hold 3+ images based on 288 x 290. For the receive side there are an additional 4 locations in the DMA pipeline. The Dynamic Driver supports both modes of operation.

The Transmit and Receive can be used in pairs for loop-back testing. HDEterm68 <u>http://www.dyneng.com/HDEterm68.html</u> can be used as a breakout for the rear panel IO. The HDEcabl68 provides a convenient cable. <u>http://www.dyneng.com/HDEcabl68.html</u> Custom cables can be manufactured to your requirements. The loop-back IO definitions are toward the end of this manual. Please contact Dynamic Engineering with your specifications.

All of the IO are routed through the FPGA to allow for custom applications that require hardware intervention or specific timing- for example an automatic address or data strobe to be generated. The initial model was register based [FLASH 0101]. Please contact Dynamic Engineering with your custom requirements. NG8 is design number "B" for the PMC-BiSerial-III with a corresponding FLASH of 0Bxx.

The IO are buffered from the FPGA with differential transceivers. The transceivers can be populated with LVDS or RS-485 compatible devices. The power plane for the transceivers is isolated to allow selectable 3.3 or 5V references for the IO. The LVDS IO requires 3.3 and 40 MHz capable RS-485 requires 5V. When mixed LVDS and RS485 are used the reference is set to 3.3 and lower speed RS-485 parts are used that are compatible with the 3.3V.

The IO are matched from the connector edge to the ball on the FPGA. The differential side is routed with controlled impedance traces. "Trace and space".

Each of the transceivers has separate direction and termination controls to allow for Any configuration of in and out, half and full duplex designs.

Each of the IO has series terminations to allow the IO to be isolated or terminated. The isolation feature is used to allow rear or front panel implementations without "stub" issues for higher speed signals.

Each IO has pull-up and pull-down options to allow half duplex lines to be set to a "marking" state when no device is on the line. The P is is ganged and the M side is too.

Each side can be set to gnd or vcc to allow a '1' or a '0' to be set on the lines. The resistors are in resistor packs and can be implemented with many values.

The terminations utilize analog switches to selectively parallel terminate the differential pair with approximately 100 ohms. It is recommended that the receiver side provide the termination.

The analog switches are protected with a DIODE on the input side of the power supply. The switches can back-feed voltage into the rest of the circuit when the PMC is powered down and the system connected to it is not. The DIODE's allow for more flexible operation and power sequencing.

The registers are mapped as 32 bit words and support 32 bit access. Most registers are read-writeable. The Windows® compatible driver is available to provide the system level interface for this version of the Biserial III. Use standard C/C++ to control your hardware or use the Hardware manual to make your own software interface. The software manual is also available on-line. Linux is available by request.

PMC-BISERIAL-III is part of the PMC Module family of modular I/O components. The PMC-BISERIAL-III conforms to the PMC standard. This guarantees compatibility with multiple PMC Carrier boards. Because the PMC may be mounted on different form factors, while maintaining plug and software compatibility, system prototyping may be done on one PMC Carrier board, with final system implementation on a different one.

PMC-BISERIAL-III can be used for multiple purposes with applications in telecommunications, control, sensors, IO, test; anywhere multiple independent or coordinated IO are useful.

PMC-BISERIAL-III features a Xilinx FPGA, and high speed differential devices. The FPGA contains the PCI interface and control required for the parallel interface.

The Xilinx design incorporates the "PCI Core" and additional modules for DMA in parallel with a direct register decoded programming model. The design model has a "base" level with the basic board level functions and "channels" which contain IO oriented functions. In the NG8 design the COM functions are designed into channels and the PLL programming, switch, and other common or basic functions are in the base design.

From a software perspective the design can be treated as "Flat" or as a hierarchy. The Dynamic Engineering Windows® driver uses the hierarchical approach to allow for more consistent software with common bit maps and offsets. The user software can control the COM pairs with the same calls and use the channel number to distinguish. This makes for consistent and easier to implement user level software.

The hardware is designed with each of the channels on a common address map – each channel has the same memory allocated to it and as much as possible the offsets within each space are defined in the same way or similar way. Again this make understanding each port easier to accomplish and less likely to have errors.

The transceivers are initialized to the receive state. Once a channel is defined via software to be a transmitter the IO are enabled and driven to the appropriate levels. Terminations are activated for ports defined to be receivers.

All the IO control and registers are instantiated within the FPGA, only the transceivers and termination switches are separate devices. If desired, the IO lines can be specially programmed to create custom timing pulses etc. Please contact Dynamic Engineering with your requirements.

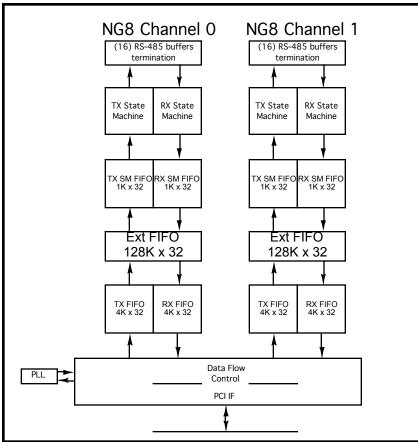

Figure 1 PMC-BISERIAL-III-NG8 Block Diagram

PMC BiSerial III NG8 features two channels each with Transmit and Receive capabilities. Each channel has separate DMA support. The internal block RAM is configured to provide FIFO's to support the DMA and IO transfer process. 4K x 32 per port to support DMA directly and 1Kx32 to support the RX or TX function. In addition the external FIFO is configured to be used for either Transmit or receive creating a large 133K x 32 FIFO.

Images size is programmable.  $288 \times 290$  is the base design size.  $288 \times 290 / 2 = LW$  required = 41760. With 133K more than 3 images can be stored for TX or RX.

The hardware has facilities to provide the overall data stored count within the three FIFO's as well as reading the counts individually. The hardware makes use of the counts to hold off starting the TX process until 1 image is stored in memory and to regulate the transfer of data between FIFO's. FIFO's have delays associated with the MT, FULL, Almost Full and Almost Empty flags plus the state-machine has a delay in reacting to the change in state. The hardware uses the counts to determine the almost full and almost empty conditions to allow the data movers to burst when not near the edge of the FIFO space and to slow down and check the flags with delays when almost empty or almost full. This way all data is moved and data in the middle moves much faster. With DMA and the levels set properly the FIFO's will operate in the middle of their ranges to properly source or receive data without overflow or under-run conditions occurring.

The hardware will pull data from the FIFO memory and store into the system memory using DMA and vice-versa. The transfer function will load the FIFO and DMA will unload. The DMA function operates at the PCI bus frequency. The transfer frequency will determine the maximum load rate into the FIFO.

The DMA programmable length is 32 bits => longer than most computer OS will allow in one segment of memory. The DMA is scatter-gather capable for longer lengths than the OS max and for OS situations where the memory is not contiguous. With Windows® lengths of 4K are common while Linux can provide much larger spaces. Larger spaces are more efficient as there are fewer initialization reads and reduced overhead on the bus. A single interrupt can control the entire transfer. Head to tail operation can also be programmed with two memory spaces with two interrupts per loop.

The hardware is organized with the IO function in channels 0 and 1 and the card level functions in the "base". The driver provides the ability to find the hardware and to allocate resources to use the base and channel functions.

|            | A B C                                 |

|------------|---------------------------------------|

| Camera IF  |                                       |

| VRef       |                                       |

| HRef       |                                       |

| BadPixel   |                                       |

| Clock      |                                       |

| Pixel Data | R0C0 R0C1 ••• R0CN R1C0 R1C1 ••• R1CN |

#### Figure 2 PMC-BISERIAL-III-NG8 Timing Diagram

With the standard rate clock [10 Mhz], the period will be 100 nS. The Clock is symmetrical with respect to the data providing 50 nS of set-up and hold minus any cable induced skew, slew time, and skew from the receiving circuit. Signals are held in the high state for a transmitter until an image is transferred. VREF, HREF, BadPixel and the Pixel Data all come from memory and can be programmed as shown or with an alternative control sequence. BadPixel in particular could be used as a 13<sup>th</sup> data bit if desired.

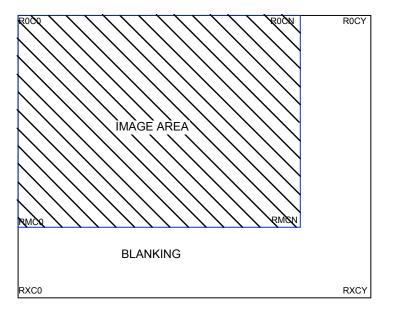

The design is programmable for LW's transferred per image. Normally there is some blanking area around the viewable area.

Figure 3 Image Dimensions

The hardware will process the data in the order stored into the FIFO. By convention the

data is organized by rows and columns. Row0Column0 is the first location broadcast and has Vref and Href set as shown in Figure 2. The pixels transmitted progress through the visible part of the image transitioning to the blanking portion at the last visible column. After the blanking at the end of the row, the next row is immediately transmitted. Href is asserted for column 0. The process repeats until the end of the visible rows is reached at which point all of the data transmitted are in the blanking area. Href is suppressed for the rows where no visible data is transmitted.

The total pixel count is the total of all of the pixels in the entire array including the blanking. (X+1)(Y+1). The programmed value is 1/2 of the total pixel count since the data is stored as long words.

A typical application may have the visible area set to 256 x 256 and the total area set to 288 x 290. This would make the blanking per row 32 pixels, and the blanking by line 34 lines.

With a 10 MHz transmit frequency the transmit time for the example above would be 8.352 mS. This comes from  $288 \times 290 \times 100 \text{ nS}$  per pixel.

With 83520 pixels per image there will be room for 3 complete images and part of a 4<sup>th</sup> in the memory for each channel.

The hardware is designed to wait for the image size to be available in memory before starting to send the first image. One images are being transmitted the image transmission continues back-to-back until the enable is disabled or the memory is empty at the start of an image.

Data is read from the FIFO lower then upper. R0C0 will be the data stored in D15-0 and R0C1 from D31-16 etc. If your system loads in the opposite order the DataOrder control bit can be used to reverse the order of the data processing.

# Address Map

| Function<br>// PMC BiSerial III NG8 definitions                                          | Offset                                                                                                                                                  |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| #define NG8_BASE_BASE<br>#define NG8_BASE_PLL_WRITE                                      | 0x0000 // 0 NG8Base Base control register<br>0x0000 // 0 NG8Base Base control register                                                                  |

| #define NG8_BASE_PLL_READ<br>#define NG8_BASE_USER_SWITCH<br>#define NG8_BASE_XILINX_REV | 0x0000 // 0 NG8Base base control register<br>0x0004 // 1 NG8Base User switch read port DIP switch read<br>0x0004 // 1 NG8Base Xilinx revision read port |

| #define NG8_BASE_XILINX_DES                                                              | 0x0004 // 1 NG8Base Xilinx design read port                                                                                                             |

| #define NG8_BASE_STATUS                                                                  | 0x0008 // 2 NG8Base status Register offset                                                                                                              |

Figure 4 PMC-BISERIAL-III Internal Address Map Base Functions

The address map provided is for the local decoding performed within PMC-BiSerial-III. The addresses are all offsets from a base address. The carrier board that the PMC is installed into provides the base address. Dynamic Engineering prefers a long-word oriented approach because it is more consistent across platforms.

The map is presented with the #define style to allow cutting and pasting into many compilers "include" files.

The host system will search the PCI bus to find the assets installed during power-on initialization. The Vendorld = 0x10EE and the CardId = 0x003F for the PMC-BiSerial-III-NG8.

The NG8 design has 2 channels implemented. The BASE contains the common elements of the design, while the Channels have the IO specific interfaces. The BASE starts at the card offset. Channel 0 starts at register 28

| Section   | Register Address Range | Port name                    |

|-----------|------------------------|------------------------------|

|           | (starting Hex address) |                              |

| Base      | 0-19 (0x0000)          | PLL, Switch, Status          |

| Channel 0 | 20-39 (0x0050)         | NG8 Camera Interface Tx & Rx |

| Channel 1 | 40-59 (0x00A0)         | NG8 Camera Interface Tx & Rx |

| Channel 0 | 20-39 (0x0050)         | NG8 Camera Interface Tx & Rx |

| Function                                              | Offset from Channel Base Address                                            |

|-------------------------------------------------------|-----------------------------------------------------------------------------|

| // PMC BiSerial III NG8 Channel definitions           |                                                                             |

| #define NG8_CHAN_CNTRL                                | 0x00000000 //0 General control register                                     |

| #dofing NC8 CHAN STATUS                               | 0x0000001 //1 Interrupt status part                                         |

| #define NG8_CHAN_STATUS<br>#define NG8 CHAN INT CLEAR | 0x00000004 //1 Interrupt status port<br>0x00000004 //1 Interrupt clear port |

| #define NGo_CHAN_INT_CLEAR                            |                                                                             |

| #define NG8 CHAN WR DMA PNTR                          | 0x00000008 //2 Write DMA physical PCI address reg                           |

| #define NG8_CHAN_TX_FIFO_COUNT                        | 0x00000008 //2 TX FIFO count read port                                      |

|                                                       |                                                                             |

| #define NG8 CHAN RD DMA PNTR                          | 0x0000000C //3 Read DMA physical PCI address reg                            |

| #define NG8_CHAN_RX_FIFO_COUNT                        | 0x0000000C //3 RX FIFO count port including pipeline                        |

|                                                       |                                                                             |

| #define NG8 CHAN FIFO                                 | 0x00000010 //4 FIFO single word access RW                                   |

| #define NG8_CHAN_TX_AMT_LVL                           | 0x00000014 //5 TX AMT level register RW, DMA FIFO                           |

| #define NG8_CHAN_RX_AFL_LVL                           | 0x00000018 //6 RX AFull level reg RW, DMA FIFO                              |

|                                                       | <b>3</b>                                                                    |

| #define NG8_CHAN_TX                                   | 0x0000001C //7 TX control register                                          |

| #define NG8_CHAN_TX_PIXEL_WORD_COUNT                  | 0x00000020 //8 TX Pixel count /2                                            |

| #define NG8_CHAN_TX_FIFO_WORD_COUNT                   | 0x00000024 //9 TX StateMachine FIFO count TX                                |

| #define NG8_CHAN_TX_AMT_LVL_TOTAL                     | 0x00000028 //10 TX AMT level control for interrupt                          |

|                                                       |                                                                             |

| #define NG8_CHAN_RX                                   | 0x0000034 //13 RX control register                                          |

|                                                       | 0x00000038 //14 RX Pixel Count Expected in words                            |

| #define NG8_CHAN_RX_FIFO_WORD_COUNT                   | 0x0000003C //15 RX StateMachine FIFO count RX                               |

| #define NG8_CHAN_RX_AFL_LVL_TOTAL                     | 0x00000040 //16 RX AFull level control for interrupt                        |

|                                                       |                                                                             |

| #define NG8_CHAN_EXT_FIFO_WORD_COUNT                  |                                                                             |

| #define NG8_CHAN_TX_WORD_COUNT                        | 0x00000048 //18 TX total data count                                         |

| HILFER NOR OLIAN DY MODD OCUNT                        | => TX DMA + EXT + TX                                                        |

| #define NG8_CHAN_RX_WORD_COUNT                        | 0x0000004C //19 RX total data count                                         |

|                                                       | => Pipeline + RX DMA + EXT + RX                                             |

|                                                       |                                                                             |

Figure 5 PMC-BISERIAL-III Channel Address Map

# Programming

Programming the PMC-BISERIAL-III-NG8 requires only the ability to read and write data in the host's PMC space.

Once the initialization process has occurred, and the system has assigned addresses to the PMC-BiSerial-III-NG8 card the software will need to determine what the address space is for the PCI interface [BAR0]. The offsets in the address tables are relative to the system assigned BAR0 base address.

The next step is to initialize the PMC-BiSerial-III-NG8. The PLL will need to be programmed to use the NG8 function. The Cypress CyberClocks software can be used to create new .JED files if desired. The PLLA should be set to the transmit reference frequency output by the Master.

The driver comes with several .JED files prepared. The driver has a utility to load the PLL and read back. The reference application software has an example of the use of PLL programming. The reference application software also includes XLATE.c which converts the .JED file from the CyberClocks tool to an array that can be programmed into the PLL.

The IO direction and termination are hardwired in this design. The ports are unidirectional and initialization is simplified with this approach.

The control bits will select how the data is transmitted – Byte ordering, size of transfer etc.

For Windows<sup>M</sup> and Linux systems the Dynamic Drivers<sup>1</sup> can be used. The driver will take care of finding the hardware and provide an easy to use mechanism to program the hardware. The Driver comes with reference software showing how to use the card and reference frequency files to allow the user to duplicate the test set-up used in manufacturing at Dynamic Engineering. Using simple, known to work routines is a good way to get acquainted with new hardware.

To use the NG8 specific functions the Channel Control, and PLL interface plus DMA will need to be programmed. To use DMA, memory space from the system should be allocated and the link list stored into memory. The location of the link list is written to the NG8 to start the DMA. Please refer to the Burst IN and Burst Out register discussions.

<sup>&</sup>lt;sup>1</sup>Currently only Windows® is supported. Please contact Dynamic Engineering for Linux.

DMA should be set-up before starting the channel port function. For transmission this will result in the FIFO being full or close to it when the transfer is started. For reception it means that the FIFO is under HW control and the delay from starting reception to starting DMA won't cause an overflow condition.

The Ready Count register can be programmed to make the HW wait until there is at least the Ready Count number of positions filled in the FIFO's before starting. When larger non-stop transfers are desired an amount close to capacity is recommended.

DMA can be programmed with a specific length. The length can be as long as you want within standard memory limitations. At the end of the DMA transfer the Host will receive an interrupt. The receiver can be stopped and the FIFO reset to clear out any extra data captured. For on-the-fly processing multiple shorter DMA segments can be programmed; at the interrupt restart DMA to point at the alternate segment to allow processing on the previous one. This technique is sometimes referred to as "ping-pong".

Other DMA notes: When DMA is operating in the receive pixels direction => writing to system memory, the PCI control signals can be used to indicate how much data is being transferred. Frame and IRDY remain asserted until the end of the requested length unless the Host asserts a STOP. In most cases a 256 word transfer is accomplished per DMA transfer with the hardware automatically generating new requests to move the data from the FIFO to the host memory. Most Bridge devices have FIFO buffers deep enough to allow for the full size DMA transfer to be accommodated resulting in a pipelined large word count transfer taking place.

In some cases the Bridge may need to be reprogrammed to do larger transfers to facilitate obtaining full bandwidth on the bus.

When operating as a transmitter the Hardware does a read from system memory and uses the same control signals to accomplish the transfer. The PMC BiSerial III NG8 can handle back-to-back max size transfers. In some cases the Bridge may need to be reprogrammed to do larger transfers to facilitate obtaining full bandwidth on the bus.

Since the request from the NG8 must pass through the bridges to the host prior to the host sourcing data, and since there is a delay in passing through the bridge, the transfer size is reduced to the Bridge prefetch length.

In addition while the host PCI controller can adsorb data at full length repeatedly, the same controller will frequently assert STOP after 16 words drastically shortening the DMA transfer. Adjusting the default for the PCI controller may also be necessary to reach proper operational data flow. The NG8 hardware has no control over the bridge or host PCI controller.

By moving the PMC BiSerial III NG8 to the first PCI bus – attached to the PCI controller all bridges are bypassed allowing 16 word transfers in the Transmit direction and 256 in the Receive direction. With a burst size of 16 the overall throughput is better than 25% which is enough to sustain 1 channel at 5 MHz effective bandwidth [10 M pixels per second].

This issue is computer dependent. Your results may be different for length of DMA achieved without making changes to the bridges between the PMC device and the system memory. BIOS can program the Bridges to operate and some may have FLASH attached to allow user "autoloading of parameters" into the configuration space control registers.

We are working on an autoloading utility for the bridges in the path and will soon offer that with our hardware products to solve the performance issue. We are also researching the PC Chip-set issue with the PCI master bridge to see what we can do to correct that as well.

# **Base Register Definitions**

# NG8\_BASE\_BASE

[\$00 parallel-io Control Register Port read/write]

| DATA BIT                                    | DESCRIPTION                                                                                                                              |  |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

| 31-21<br>20<br>19<br>18<br>17<br>16<br>15-0 | spare<br>bit 19 read-back of pll_dat register bit<br>pll_dat [write to PLL, read-back from PLL]<br>pll_s2<br>pll_sclk<br>pll_en<br>spare |  |

#### Figure 6 PMC-BISERIAL-III Control Base Register Bit Map

This is the base control register for the PMC BiSerial III NG8. The features common to all channels are controlled from this port. Unused bits are reserved for additional new features. Unused bits should be programmed '0' to allow for future commonality.

pll\_en: When this bit is set to a one, the signals used to program and read the PLL are enabled.

pll\_sclk/pll\_dat : These signals are used to program the PLL over the I<sup>2</sup>C serial interface. Sclk is always an output whereas Sdata is bi-directional. This register is where the Sdata output value is specified or read-back.

pll\_s2: This is an additional control line to the PLL that can be used to select additional pre-programmed frequencies. Set to '0' for most applications.

The PLL is programmed with the output file generated by the Cypress PLL programming tool. [CY3672 R3.01 Programming Kit or CyberClocks R3.20.00 Cypress may update the revision from time to time.] The .JED file is used by the Dynamic Driver to program the PLL. Programming the PLL is fairly involved and beyond the scope of this manual. For clients writing their own drivers it is suggested to get the Engineering Kit for this board including software, and to use the translation and programming files ported to your environment. This procedure will save you a lot of time. For those who want to do it themselves the Cypress PLL in use is the 22393. The output file from the Cypress tool can be passed directly to the Dynamic Driver [Linux or Windows] and used to program the PLL without user intervention.

The reference frequency for the PLL is 50 MHz.

# NG8\_BASE\_ID

[\$04 Switch and Design number port read only]

|       | DESCRIPTION            |

|-------|------------------------|

| 31-24 | spare                  |

| 23-8  | Design ID and Revision |

| 7-0   | DIP switch             |

|       |                        |

#### Figure 7 PMC-BISERIAL-III ID and Switch Bit Map

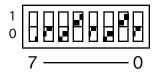

The DIP Switch is labeled for bit number and '1' '0' in the silk screen. The DIP Switch can be read from this port and used to determine which PMC BiSerial III physical card matches each PCI address assigned in a system with multiple cards installed. The DIPswitch can also be used for other purposes – software revision etc. The switch shown would read back 0x12.

The Design ID and Revision are defined by a 16 bit field allowing for 256 designs and 256 revisions of each. The NG8 design is 0x0B the current revision is 0x01.

The PCI revision is updated in HW to match the design revision. The board ID will be updated for major changes to allow drivers to differentiate between revisions and applications.

### NG8\_BASE\_STATUS

[\$08 Board level Status Port read only]

| DATA BIT      | DESCRIPTION                              |  |

|---------------|------------------------------------------|--|

| 31-12<br>11-8 | Set to '0'<br>Reserved for PLL status    |  |

| 7-2<br>1      | set to '0'<br>Masked Channel 1 Interrupt |  |

| 0             | Masked Channel 0 Interrupt               |  |

Figure 8 PMC-BISERIAL-III Status Port Bit Map

**Channel Interrupt** – The local masked interrupt status from the channel. Each channel can have different interrupt sources. DMA Write or DMA Read or IntForce or TX/RX request are typical sources. Polling can be accomplished using the channel status register and leaving the channel interrupt disabled.

# **Channel Register Definitions**

#### Channel Bit Maps

The NG8 design has 2 channels. The basic control signals are the same for the channel base, channel status, FIFO and DMA interfaces. The following descriptions will be in the form of a common feature description for each address and then differences if any for each channel.

#### Notes:

The offsets shown are relative to the channel base address not the card base address.

# NG8\_CHAN\_CNTRL

[0x0] Channel Control Register (read/write)

| Channel Control Register |                            |  |  |  |

|--------------------------|----------------------------|--|--|--|

| Data Bit                 | Description                |  |  |  |

| 31-16                    | spare                      |  |  |  |

| 15                       | Direction TX/RX            |  |  |  |

| 14                       | ExtFifoMux RX/TX           |  |  |  |

| 13                       | ExtFifoEn                  |  |  |  |

| 12                       | ExtFifoLoad                |  |  |  |

| 11-9                     | Spare                      |  |  |  |

| 8                        | OutUrgent                  |  |  |  |

| 7                        | InUrgent                   |  |  |  |

| 6                        | Read DMA Interrupt Enable  |  |  |  |

| 5                        | Write DMA Interrupt Enable |  |  |  |

| 4                        | Force Interrupt            |  |  |  |

| 3                        | Channel Interrupt Enable   |  |  |  |

| 2                        | Bypass                     |  |  |  |

| 1                        | RX FIFO Reset              |  |  |  |

| 0                        | TX FIFO Reset              |  |  |  |

|                          |                            |  |  |  |

Figure 9 PMC-BISERIAL-III channel Control Register

<u>FIFO TX/RX Reset</u>: When set to a one, the transmit and/or receive FIFO's will be reset. When these bits are zero, normal FIFO operation is enabled. In addition the TX and RX State Machine is also reset.

Write/Read DMA Interrupt Enable: These two bits, when set to one, enable the

interrupts for DMA writes and reads respectively.

<u>Channel Interrupt Enable</u>: When this bit is set to a one, all enabled interrupts (except the DMA interrupts) will be gated through to the PCI interface level of the design; when this bit is a zero, the interrupts can be used for status without interrupting the host. The channel interrupt enable is for the channel level interrupt sources only.

<u>Force Interrupt</u>: When this bit is set to a one, a system interrupt will occur provided the Channel Interrupt and master interrupt enables are set. This is useful for interrupt testing.

<u>InUrgent / OutUrgent</u> when set causes the DMA request to have higher priority under certain circumstances. Basically when the TX FIFO is almost empty and InUrgent is set the TX DMA will have higher priority than it would otherwise get. Similarly if the RX FIFO is almost full and OutUrgent is set the read DMA will have higher priority. The purpose is to allow software some control over how DMA requests are processed and to allow for a higher rate channel to have a higher priority over other lower rate channels.

<u>ByPass</u> when set allows the FIFO to be used in a loop-back mode internal to the device. A separate state-machine is enabled when ByPass is set and the TX and RX are not enabled. The state-machine checks the TX and RX FIFO's and when not empty on the TX side and not Full on the RX side moves data between them. Writing to the TX FIFO allows reading back from the RX side. An example of this is included in the Driver reference software.

<u>ExtFifoEn</u>: When cleared to a zero, the External FIFO will be reset. When set the External FIFO is enabled. The channels have external 128Kx32 FIFO's attached. Please note that the state of the Load pin how the part comes out of reset – what the default Almost Full and Almost Empty offsets are.

<u>ExtFifoLoad</u>: The external FIFO's have a LOAD pin which is tied directly to this register bit. The FIFO's in use are IDT72V36110. This is a dual purpose pin. During Master Reset, the state of the LD input determines the default offset values for the PAE and PAF flags selected. After Master Reset, this pin enables writing to and reading from the offset registers.

With ExtFifoLoad low during reset the default offset is 127. With ExtFifoLd high during reset the default offset is 1023. The offset is from the end of the FIFO. For example the PAE flag would be set to be 127, with the level of the FIFO 127 and less the PAE flag would be asserted. With 128K – 127 and more the PAF flag will be asserted.

In addition if the flags are to be reprogrammed using the parallel load feature the load pin should be low during reset Setting low allows writes to the FIFO to load new values

into the FIFO. Taking Load high again puts the FIFO back into Data mode.

The FIFO's are configured with 32 in and 32 out. To parallel load the offset registers the PAE value is written first and the PAF value written second. Both values must be written to properly load. The values can be read back with the load pin low.

The data for the flags will flow through the TX DMA FIFO to the external FIFO. It is important to clear the FIFO's via reset prior to programming the offset registers to reset the pointer for the registers and to make sure the data written through the DMA FIFO is what is loaded into the External FIFO. Please also see ExtFifoMux control. The mux needs to be set to TX.

<u>ExtFifoMux</u>: bit controls if data is moved from the TX DMA FIFO or from the RX side into the External FIFO. '0' selects the TX path and '1' selects the RX path.

<u>Direction</u>: is used to select TX or RX operation for the IO. The direction bit is independent of the state-machines. Setting to 1 selects transmit operation and clearing to 0 selects RX operation for the transceivers assigned to the channel plus enables the terminations in the case of RX.

| [0x4 | ] Channel | Status | Read/Clear | Latch | Write Port |

|------|-----------|--------|------------|-------|------------|

|------|-----------|--------|------------|-------|------------|

| Channel Status Register |                              |  |

|-------------------------|------------------------------|--|

| Data Bit                | Description                  |  |

| 31                      | Interrupt Status             |  |

| 30                      | Local Int                    |  |

| 29                      | spare                        |  |

| 28                      | Direction                    |  |

| 27                      | Ext FIFO Full                |  |

| 26                      | Ext FIFO AFull               |  |

| 25                      | Ext FIFO AMT                 |  |

| 24                      | Ext FIFO MT                  |  |

| 23                      | Burst In Idle [write]        |  |

| 22                      | Burst Out Idle [read]        |  |

| 21                      | TX Idle State                |  |

| 20                      | RX Idle State                |  |

| 19                      | TX UnderFLow Err Lat         |  |

| 18                      | RX OverFlow Err Lat          |  |

| 17                      | RX Image Complete            |  |

| 16                      | TX Image Complete            |  |

| 15                      | Read DMA Interrupt Occurred  |  |

| 14                      | Write DMA Interrupt Occurred |  |

| 13                      | Read DMA Error Occurred      |  |

| 12                      | Write DMA Error Occurred     |  |

| 11                      | RX AFull Int Lat             |  |

| 10                      | TX AMT Int Lat               |  |

| 9                       | RX AFull Int Lvl             |  |

| 8                       | TX AMT Int Lvl               |  |

| 7                       | spare                        |  |

| 6                       | RX DMA FIFO Full             |  |

| 5                       | RX DMA FIFO Almost Full      |  |

| 4                       | RX DMA FIFO Empty            |  |

| 3                       | Spare                        |  |

| 2                       |                              |  |

| 1                       | Tx DMA FIFO Almost Empty     |  |

| 0                       | Tx DMA FIFO Empty            |  |

Figure 10 PMC-BiSerial-III Channel STATUS PORT

**NG8 FIFO:** Two 4K x 32 FIFO's are used to create the internal Transmit and Receive DMA FIFO's. The FIFO's are tied to the PCI bus to enable burst operations for DMA.

The status for the Transmit FIFO and Receive FIFO refer to these FIFO's. The status is active high. 0x13 would correspond to empty Transmitter and empty Master internal FIFO's.

Please note with the Receive side status; the status reflects the state of the FIFO and does not take the 4 deep pipeline into account. For example the FIFO may be empty and there may be valid data within the pipeline. The data count with the combined FIFO and pipeline value and can also be used for read size control. [see later in register descriptions]

<u>RX FIFO Empty</u>: When a one is read, the FIFO contains no data; when a zero is read, there is at least one data word in the FIFO.

<u>RX FIFO Almost Full</u>: When a one is read, the number of data words in the data FIFO is greater than the value written to the corresponding RX\_AFL\_LVL register; when a zero is read, the FIFO level is less than that value.

<u>RX FIFO Full</u>: When a one is read, the receive data FIFO is full; when a zero is read, there is room for at least one more data-word in the FIFO.

<u>TX FIFO Empty</u>: When a one is read, the FIFO contains no data; when a zero is read, there is at least one data word in the FIFO.

<u>TX FIFO Almost Empty</u>: When a one is read, the number of data words in the data FIFO is less than or equal to the value written to the corresponding TX\_AMT\_LVL register; when a zero is read, the FIFO level is more than that value.

<u>TX FIFO Full</u>: When a one is read, the receive data FIFO is full; when a zero is read, there is room for at least one more data-word in the FIFO.

<u>TX AMT Int Lvl</u>: is set when the combined FIFO contents count is below the Almost Empty level total programmed into the reference register.

<u>RX AFull Int LvI</u>: is set when the combined FIFO contents count is above the Almost Full Level Total programmed into the reference register.

<u>TX AMT Int Lat</u>: is set when the TX DMA FIFO contents count has been above the almost empty level and has transitioned below that level. This bit is a sticky bit and is held until cleared by writing back to this address with this bit set.

<u>RX AFull Int Lat</u>: is set when the RX DMA FIFO contents count has been below the almost full level and has transitioned above that level. This bit is a sticky bit and is held until cleared by writing back to this address with this bit set.

<u>Write/Read DMA Error Occurred</u>: When a one is read, a write or read DMA error has been detected. This will occur if there is a target or master abort or if the direction bit in the next pointer of one of the chaining descriptors is incorrect. A zero indicates that no write or read DMA error has occurred. These bits are latched and can be cleared by writing back to the Status register with a one in the appropriate bit position.

<u>Write/Read DMA Interrupt Occurred</u>: When a one is read, a write/read DMA interrupt is latched. This indicates that the scatter-gather list for the current write or read DMA has completed, but the associated interrupt has yet to be processed. A zero indicates that no write or read DMA interrupt is pending.

<u>TX Image Complete:</u> This bit is set at the completion of the transmission of an image. This is a sticky bit and can be cleared by writing back with this bit position set. The interrupt can be used as a timer based on the image size or to help with flow control when using larger DMA transfers with multiple images.

<u>RX Image Complete:</u> This bit is set at the completion of the reception of an image. This is a sticky bit and can be cleared by writing back with this bit position set. The interrupt can be used as a timer based on the image size or to help with flow control when using larger DMA transfers with multiple images.

<u>RX Over Flow:</u> This bit is set if the RX SM FIFO is full when it is time to write another pixel pair. The data movers operate at a higher frequency than the receiver which means that the DMA and External FIFO's will be backed up before this error can occur. This is a sticky bit and requires a write back with this bit set to clear.

<u>TX Under Flow</u>: This bit is set if the TX SM FIFO is empty when it is time to read another pixel pair. The data movers operate at a higher frequency than the transmitter which means that the DMA and External FIFO's will be empty up before this error can occur. This is a sticky bit and requires a write back with this bit set to clear.

<u>RX IDLE</u> is set when the state-machine is in the idle state. When lower clock rates are used it may take a while to clean-up and return to the idle state. If SW has cleared the start bit to terminate the data transfer; SW can use the IDLE bit to determine when the HW has completed its task and returned.

<u>TX IDLE</u> is set when the state-machine is in the idle state. When lower clock rates are used it may take a while to clean-up and return to the idle state. If SW has cleared the start bit to terminate the transfer; SW can use the IDLE bit to determine when the HW has completed its task and returned.

<u>BO and BI Idle</u> are Burst Out and Burst In IDLE state status for the Receive and Transmit DMA actions. The bits will be 1 when in the IDLE state and 0 when processing a DMA. A new DMA should not be launched until the State machine is back in the IDLE state. Please note that the direction implied in the name has to do with the DMA direction – Burst data into the card for Transmit and burst data out of the card for Receive.

EXT FIFO MT: is set when the external FIFO is empty, when 0 at least 1 data is stored into the external FIFO.

<u>EXT FIFO AMT</u>: is set when the external FIFO is almost empty, when 0 more than the Almost Empty threshold is stored into the external FIFO. The threshold is programmable. Please refer to the channel control definition for more programming information.

<u>EXT FIFO AFull</u>: is set when the external FIFO is Almost Full, when 0 less than the Almost Full threshold is stored into the external FIFO. The threshold is programmable. Please refer to the channel control definition for more programming information.

<u>EXT FIFO Full</u>: is set when the external FIFO is full, when 0 at least 1 data position is available for new data to be stored into the external FIFO.

<u>Local Interrupt</u> is the masked combined interrupt status for the channel not including DMA. The status is before the master interrupt enable for the channel.

Interrupt Status is the combined Local Interrupt with DMA and the master interrupt enable. If this bit is set this channel has a pending interrupt request.

#### NG8\_CHAN\_WR\_DMA\_PNTR

[0x08] Write DMA Pointer (write only)

| BurstIn DMA Pointer Address Register |                                            |  |

|--------------------------------------|--------------------------------------------|--|

| Data Bit                             | Description                                |  |

| 31-2                                 | First Chaining Descriptor Physical Address |  |

| 1                                    | direction [0]                              |  |

| 0                                    | end of chain                               |  |

#### Figure 11 PMC-BiSerial-III Write DMA pointer register

This write-only port is used to initiate a scatter-gather write [TX] DMA. When the address of the first chaining descriptor is written to this port, the DMA engine reads three successive long words beginning at that address. Essentially this data acts like a chaining descriptor value pointing to the next value in the chain.

The first is the address of the first memory block of the DMA buffer containing the data to read into the device, the second is the length in bytes of that block, and the third is the address of the next chaining descriptor in the list of buffer memory blocks. This process is continued until the end-of-chain bit in one of the next pointer values read indicates that it is the last chaining descriptor in the list.

All three values are on LW boundaries and are LW in size. Addresses for successive parameters are incremented. The addresses are physical addresses the HW will use on the PCI bus to access the Host memory for the next descriptor or to read the data to be transmitted. In most OS you will need to convert from virtual to physical. The length parameter is a number of bytes, and must be on a LW divisible number of bytes.

Status for the DMA activity can be found in the channel control register and channel status register.

Notes:

- 1. Writing a zero to this port will abort a write DMA in progress.

- 2. End of chain should not be set for the address written to the DMA Pointer Address Register. End of chain should be set when the descriptor follows the last length parameter.

- 3. The Direction should be set to '0' for Burst In DMA in all chaining descriptor locations.

### NG8\_CHAN\_TX\_FIFO\_COUNT

[0x08] TX [Target] FIFO data count (read only)

|          | TX FIFO Data Count Port |

|----------|-------------------------|

| Data Bit | Description             |

| 31-16    | Spare                   |

| 15-0     | TX Data Words Stored    |

#### Figure 12 PMC-BiSerial-III Transmit DMA FIFO data count Port

This read-only register port reports the number of 32-bit data words in the Transmit DMA FIFO. This design has 4095 locations possible. Unused bits within the count word are set to '0'. The spare bits are not driven and should be masked.

#### NG8\_CHAN\_RD\_DMA\_PNTR

[0x0C] Read DMA Pointer (write only)

| BurstIn DMA Pointer Address Register |                                            |  |

|--------------------------------------|--------------------------------------------|--|

| Data Bit                             | Description                                |  |

| 31-2                                 | First Chaining Descriptor Physical Address |  |

| 1                                    | direction [1]                              |  |

| 0                                    | end of chain                               |  |

#### Figure 13 PMC-BiSerial-III Read DMA pointer register

This write-only port is used to initiate a scatter-gather read [RX] DMA. When the address of the first chaining descriptor is written to this port, the DMA engine reads three successive long words beginning at that address. Essentially this data acts like a chaining descriptor value pointing to the next value in the chain.

The first is the address of the first memory block of the DMA buffer to write data from the device to, the second is the length in bytes of that block, and the third is the address of the next chaining descriptor in the list of buffer memory blocks. This process is continued until the end-of-chain bit in one of the next pointer values read indicates that it is the last chaining descriptor in the list.

All three values are on LW boundaries and are LW in size. Addresses for successive parameters are incremented. The addresses are physical addresses the HW will use on the PCI bus to access the Host memory for the next descriptor or to read the data to be transmitted. In most OS you will need to convert from virtual to physical. The length parameter is a number of bytes, and must be on a LW divisible number of bytes.

Status for the DMA activity can be found in the channel control register and channel status register.

Notes:

- 1. Writing a zero to this port will abort a write DMA in progress.

- 2. End of chain should not be set for the address written to the DMA Pointer Address Register. End of chain should be set when the descriptor follows the last length parameter.

- 3. The Direction should be set to '1' for Burst Out DMA in all chaining descriptor locations.

# NG8\_CHAN\_RX\_FIFO\_COUNT

[0x0C] RX [Master] FIFO data count (read only)

|          | RX FIFO Data Count Port |

|----------|-------------------------|

| Data Bit | Description             |

| 31-16    | Spare                   |

| 15-0     | RX Data Words Stored    |

#### Figure 14 PMC-BiSerial-III Receive DMA FIFO data count Port

This read-only register port reports the number of 32-bit data words in the Receive FIFO plus pipeline. The maximum count is the FIFO size plus 4 = 0x1003. The upper unused data bits within the word are set to '0' by HW. The spare bits are not driven and should be masked.

# NG8\_CHAN\_FIFO

[0x10] Write TX/Read RX FIFO Port

| RX [Master] and TX [Target] FIFO Port |                |  |

|---------------------------------------|----------------|--|

| Data Bit                              | Description    |  |

| 31-0                                  | FIFO data word |  |

### Figure 15 PMC-BiSerial-III RX/TX FIFO Port

This port is used to make single-word accesses from the FIFO. Data read from this port will no longer be available for DMA transfers. Writing to the port loads the Transmit FIFO, Reading unloads the Receive FIFO.

# NG8\_CHAN\_TX\_AMT\_LVL

[0x14] Transmit almost-empty level (read/write)

| Target Aln                | nost-Full Level Register                           |

|---------------------------|----------------------------------------------------|

| Data Bit<br>31-16<br>15-0 | Description<br>Spare<br>TX FIFO Almost-Empty Level |

#### Figure 16 PMC-BiSerial-III Transmit ALMOST EMPTY LEVEL register

This read/write port accesses the almost-empty level register for the DMA FIFO. When the number of data words in the transmit DMA FIFO is less than than this value, the almost-empty status bit will be set. The register is R/W for 16 bits. The mask is valid for a size matching the depth of the FIFO. 4k x32 is the TX FIFO for a 12 bit valid count range [11-0].

### NG8\_CHAN\_RX\_AFL\_LVL

[0x18] Receive almost-full (read/write)

| Mast                      | ter Almost-Full Level Register                    |  |

|---------------------------|---------------------------------------------------|--|

| Data Bit<br>31-16<br>15-0 | Description<br>Spare<br>RX FIFO Almost-Full Level |  |

#### Figure 17 PMC-BiSerial-III Receive ALMOST FULL LEVEL register

This read/write port accesses the almost-full level register. When the number of data words in the receive DMA FIFO is equal or greater than this value, the almost-full status bit will be set. The register is R/W for 16 bits. The mask is valid for a size matching the depth of the FIFO.  $4k \times 32 + 4$  is the Master FIFO size for a 13 bit valid count range [12-0]. The level includes the pipeline for an additional 4 locations [0xFFF + 4 = 0x1003].

# NG8\_CHAN\_TX\_CNTRL

| Channel Control Register |              |  |

|--------------------------|--------------|--|

| Data Bit                 | Description  |  |

| 6                        | TxAeLvIIntEn |  |

| 5                        | TxPixelOrder |  |

| 4                        | TxUnFIEn     |  |

| 3                        | TxAeIntEn    |  |

| 2                        | TxIntEn      |  |

| 1                        | TxFifoEn     |  |

| 0                        | TxEn         |  |

|                          |              |  |

[0x1C] Channel Transmitter Control Register (read/write)

#### Figure 18 PMC-BISERIAL-III Channel Transmitter Control Register

**TxEn** when set causes the Transmit State Machine to begin operation. The transmitter will wait until there is sufficient data in the FIFO pipeline to begin operation. This is a programmable number and can be adjusted based on image size and scheme of operation. For continuous transmission it is recommended to set this value to several images to allow the pipeline to be almost full before starting.

**TxFifoEn** when set enables the local Tx FIFO to read data from the external FIFO and transfer it to the Tx State Machine FIFO. Enable for TX operation, Disable for RX operation.

**TxIntEn** when set enables an interrupt to be generated for each image transmitted. The status and interrupt are set each time an image is completed.

**TxAeIntEn** when set enables an interrupt to be generated when the FIFO level has been more than Almost Empty and becomes Almost Empty. The status is a sticky bit and retains the information until cleared. The Status and interrupt is reasserted each time the transition occurs.

**TxUnFIEn** when set enables the interrupt from an underflow condition. The underflow status bit is set when the transmitter is ready to read the next pixel pair and the FIFO is empty. The status is a sticky bit and held until cleared. The underflow status is masked with TxUnFIEn to create the interrupt. Clear by clearing this bit or clearing the status [preferred].

**TxPixelOrder** when cleared uses the PCI standard for word ordering and when set reverses the word order. Each pixel is 1 word long. Two pixels are stored per long

word transferred across the PCI bus. When cleared the data on D15-0 are used first and the data on D31-16 are used second.

**TxAeLvIIntEn** when set enables the interrupt based on the Almost Empty condition. When the interrupt occurs a programmable amount of data is left in the FIFO. The interrupt can be used to request a new DMA for a new image to be transferred or for other purposes. Larger DMA transfers spanning multiple images are recommended for continuous operation.

### NG8\_CHAN\_TX\_PIXEL\_WORD\_COUNT

[0x20] TX Pixels to send per image count

| TX Pixels per Image Definition |                                      |  |

|--------------------------------|--------------------------------------|--|

| Data Bit<br>31-0               | Description<br>TX Pixels/2 per Image |  |

Figure 19 PMC-BiSerial-III Transmit Pixel Count Port

This read-write register port holds the number of Pixels to transmit per image. Please note that the count is in Pixels/2 since it is used for the number of LW to transmit.

# NG8\_CHAN\_TX\_FIFO\_WORD\_COUNT

[0x24] TX State Machine FIFO data count (read only)

|          | TX State Machine FIFO Level |

|----------|-----------------------------|

| Data Bit | Description                 |

| 31-16    | Spare                       |

| 15-0     | TX Data Count in SM FIFO    |

### Figure 20 PMC-BiSerial-III TARGET DATA COUNT Port

The 1Kx32 FIFO between the External FIFO and the State-Machine is used for rate matching and local data storage for the TX state machine. The amount data stored in the FIFO can be read from this port. The clock reference to the FIFO is not the PCI clock. Reading this port while the level is changing can result in incorrect values. The values are correct when static. For example if the system is pre-filled before the TX side is enabled.

# NG8\_CHAN\_TX\_AMT\_LVL\_TOTAL

[0x28] TX Almost Empty Level Control Register

|          | TX Interrupt Level                          |

|----------|---------------------------------------------|

| Data Bit | Description                                 |

| 31-0     | Number of words in FIFO for AMT level check |

#### Figure 21 PMC-BiSerial-III TX AMT Level Control Port

This register defines a comparison against the TX FIFO path. The TX DMA FIFO Plus the External FIFO plus the TX SM FIFO counts are added together and compared with the value programmed into this register. When the value of the count is less than the value of the register the AMT level interrupt can be asserted. The control register has the enable for the interrupt. The status register has the AMT Level Interrupt status.

### NG8\_CHAN\_TX\_READY\_COUNT

[0x2C] TX Ready Count Control Register

| TX Ready Count |                                      |  |  |

|----------------|--------------------------------------|--|--|

| Data Bit       | Description                          |  |  |

| 31-0           | Number of words in FIFO for TX start |  |  |

#### Figure 22 PMC-BiSerial-III TX Ready Count Control Port

This register defines a comparison against the TX FIFO path. The TX DMA FIFO Plus the External FIFO plus the TX SM FIFO counts are added together and compared with the value programmed into this register. When the value of the count is less than the value of the register the start of transmission is held off. The purpose is to allow the DMA to pre-fill the FIFO chain prior to starting transmission and to allow the software to perform one large DMA transfer instead of doing a prefill, start TX and then an additional DMA. The level should be set to match the size of the image data to send up to the total FIFO size. For 1 image set to a single image size, for two set to two etc. In the example case three images can be held within the FIFO chain.

The TX state machine also waits for the local FIFO to be almost full. The requirement for the local FIFO will put a lower bound on the image size of approximately 2K pixels. If your application requires smaller images please contact the factory. 2K in square form would be 45 x 45 including all visible and blanking areas.

# NG8\_CHAN\_RX\_CNTRL

[0x34] Channel Receiver Control Register (read/write)

| Channel Control Register |               |  |  |

|--------------------------|---------------|--|--|

| Data Bit                 | Description   |  |  |

| 10                       | RxFifoPathEn  |  |  |

| 9-7                      | Spare         |  |  |

| 6                        | RxAflLvIIntEn |  |  |

| 5                        | RxPixelOrder  |  |  |

| 4                        | RxOvFIEn      |  |  |

| 3                        | RxAfIntEn     |  |  |

| 2                        | RxIntEn       |  |  |

| 1                        | Spare         |  |  |

| 0                        | RxEn          |  |  |

|                          |               |  |  |

#### Figure 23 PMC-BISERIAL-III Channel Receiver Control Register

**RxEn** when set causes the Receiver State Machine to begin operation. The Receive state machine will begin searching for the 0,0 Pixel with both HREF and VREF asserted. The image will begin capture with the 0,0 pixel and be loaded based on the received clock until stopped by software.

The received clock is sampled. If the clock is not present or stops the hardware will wait for the clock to continue. Pausing the clock can in effect pause the transfer without changing the pixel data transferred. At the end of the programmed image size, the hardware will look for 0,0. It is expected to be the next pixel received after the end of the previous image [including the blanking].

If the image size does not match the image received the following image may be skipped or the current image truncated depending on the direction of the mismatch.

**RxIntEn** when set causes an interrupt for each image captured. This interrupt can be used to read each image sequentially as they are received. Alternatively the programmable level interrupt can be used based on data within the FIFO. For continuous operation larger multi-image DMA transfers are recommended.

**RxAfIntEn** when set enables an interrupt to be generated when the FIFO level has been less than Almost Full and becomes Almost Full. The status is a sticky bit and retains the information until cleared. The Status and interrupt is reasserted each time the transition occurs.

**RxOvFIEn** when set causes an interrupt when the Rx FIFO overflows. The FIFO is considered to be in an OverFLow condition if it is full when it is time to write the next Pixel pair.