DYNAMIC ENGINEERING 150 DuBois, Suite C Santa Cruz, CA 95060 (831) 457-8891 Fax (831) 457-4793 <u>http://www.dyneng.com</u> <u>sales@dyneng.com</u> Est. 1988

**User Manual**

# **PMC-BISERIAL-III BAE9**

## Eight-Channel UART Interface PMC Module

Revision B1 Corresponding Hardware: Revision D, E 10-2005-0204/0205 Corresponding Firmware: Revision E

#### PMC-BiSerial-III BAE9

Eight-Channel PMC Based UART Interface

Dynamic Engineering 150 DuBois, Suite C Santa Cruz, CA 95060 (831) 457-8891 FAX: (831) 457-4793

©2012, 2013 by Dynamic Engineering. Other trademarks and registered trademarks are owned by their respective manufactures. Manual Revision B1 Revised February 26, 2013 This document contains information of proprietary interest to Dynamic Engineering. It has been supplied in confidence and the recipient, by accepting this material, agrees that the subject matter will not be copied or reproduced, in whole or in part, nor its contents revealed in any manner or to any person except to meet the purpose for which it was delivered.

Dynamic Engineering has made every effort to ensure that this manual is accurate and complete. Still, the company reserves the right to make improvements or changes in the product described in this document at any time and without notice. Furthermore, Dynamic Engineering assumes no liability arising out of the application or use of the device described herein.

The electronic equipment described herein generates, uses, and can radiate radio frequency energy. Operation of this equipment in a residential area is likely to cause radio interference, in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Dynamic Engineering's products are not authorized for use as critical components in life support devices or systems without the express written approval of the president of Dynamic Engineering.

Connection of incompatible hardware is likely to cause serious damage.

## Table of Contents

| PRODUCT DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 6                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| THEORY OF OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10                                                                                                                                                              |

| PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 13                                                                                                                                                              |

| ADDRESS MAP (BAR 0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 14                                                                                                                                                              |

| ADDRESS MAP (BAR 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                                                                                                                              |

| Register Definitions<br>BAE9_BASE_CONTROL<br>BAE9_USER_SWITCH<br>BAE9_CHAN_0-7_CONTROL<br>BAE9_CHAN_0-7_STATUS<br>BAE9_CHAN_0-7_WR_DMA_PNTR<br>BAE9_CHAN_0-7_RD_DMA_PNTR<br>BAE9_CHAN_0-7_RD_DMA_PNTR<br>BAE9_CHAN_0-7_RX_ADDRESS<br>BAE9_CHAN_0-7_RX_ADDRESS<br>BAE9_CHAN_0-7_TRIG_CNT_LAT<br>BAE9_CHAN_0-7_TRIG_HICNT_OUT<br>BAE9_CHAN_0-7_TRIG_LOCNT_OUT<br>BAE9_CHAN_0-7_TX_CONTROL<br>BAE9_CHAN_0-7_RX_CONTROL<br>BAE9_CHAN_0-7_TX_START_LATCH<br>BAE9_CHAN_0-7_RX_START_LATCH<br>BAE9_CHAN_0-7_RX_BYTE_COUNT | <b>17</b><br>17<br>18<br>19<br>20<br>22<br>23<br>23<br>23<br>24<br>24<br>24<br>24<br>25<br>26<br>26<br>26<br>26<br>27<br>28<br>30<br>32<br>33<br>33<br>33<br>33 |

| Loop-back<br>Full-Duplex Loop-Back<br>Half-Duplex Loop-Back                                                                                                                                                                                                                                                                                                                                                                                                                                                        | <b>35</b><br>35<br>36                                                                                                                                           |

| PMC PCI PN1 INTERFACE PIN ASSIGNMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 37                                                                                                                                                              |

| PMC PCI PN2 INTERFACE PIN ASSIGNMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 38                                                                                                                                                              |

| FRONT PANEL I/O PIN ASSIGNMENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39                                                                                                                                                              |

**Embedded Solutions**

| APPLICATIONS GUIDE                        | 40              |

|-------------------------------------------|-----------------|

| Interfacing                               | 40              |

| CONSTRUCTION AND RELIABILITY              | 41              |

| THERMAL CONSIDERATIONS                    | 41              |

| WARRANTY AND REPAIR                       | 41              |

| Service Policy<br>Out of Warranty Repairs | <b>42</b><br>42 |

| For Service Contact:                      | 42              |

| SPECIFICATIONS                            | 43              |

| ORDER INFORMATION                         | 44              |

| SCHEMATICS                                | 44              |

## List of Figures

| FIGURE 1<br>FIGURE 2 | PMC-BISERIAL-III BLOCK DIAGRAM<br>PMC-BISERIAL-III BAE9 BLOCK DIAGRAM | 6<br>7 |

|----------------------|-----------------------------------------------------------------------|--------|

| FIGURE 3             | PMC-BISERIAL-III BAE9 REGISTER ADDRESS MAP                            | 14     |

| FIGURE 3             | PMC-BISERIAL-III BAE9 REGISTER ADDRESS MAP (CONTINUED)                | 15     |

| FIGURE 4             | PMC-BISERIAL-III BAE9 MEMORY BLOCK ADDRESS MAP                        | 16     |

| FIGURE 5             | PMC-BISERIAL-III BAE9 BASE CONTROL                                    | 17     |

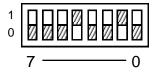

| FIGURE 6             | PMC-BISERIAL-III BAE9 USER SWITCH PORT                                | 18     |

| FIGURE 7             | PMC-BISERIAL-III BAE9 CHANNEL CONTROL                                 | 19     |

| FIGURE 8             | PMC-BISERIAL-III BAE9 CHANNEL STATUS                                  | 20     |

| FIGURE 9             | PMC-BISERIAL-III BAE9 WRITE DMA POINTER                               | 22     |

| FIGURE 10            | PMC-BISERIAL-III BAE9 TX RAM ADDRESS OFFSETS                          | 23     |

| FIGURE 11            | PMC-BISERIAL-III BAE9 READ DMA POINTER                                | 23     |

| FIGURE 12            | PMC-BISERIAL-III BAE9 RX RAM ADDRESS OFFSETS                          | 24     |

| FIGURE 13            | PMC-BISERIAL-III BAE9 RX/TX I/O START ADDRESS                         | 24     |

| FIGURE 14            | PMC-BISERIAL-III BAE9 TRIGGER MONITOR COUNTS                          | 25     |

| FIGURE 15            | PMC-BISERIAL-III BAE9 TRIGGER MONITOR ON COUNTS                       | 26     |

| FIGURE 16            | PMC-BISERIAL-III BAE9 TRIGGER MONITOR OFF COUNTS                      | 26     |

| FIGURE 17            | PMC-BISERIAL-III BAE9 DISCRETE OUTPUT PARAMETERS                      | 27     |

| FIGURE 18            | PMC-BISERIAL-III BAE9 TX CONTROL                                      | 28     |

| FIGURE 19            | PMC-BISERIAL-III BAE9 RX CONTROL                                      | 30     |

| FIGURE 20            | PMC-BISERIAL-III BAE9 TX UART PARAMETERS                              | 32     |

| FIGURE 21            | PMC-BISERIAL-III BAE9 TX START LATCH                                  | 33     |

| FIGURE 22            | PMC-BISERIAL-III BAE9 RX START LATCH                                  | 33     |

| FIGURE 23            | PMC-BISERIAL-III BAE9 RX BYTE COUNT                                   | 34     |

| FIGURE 24            | PMC-BISERIAL-III BAE9 PN1 INTERFACE                                   | 37     |

| FIGURE 25            | PMC-BISERIAL-III BAE9 PN2 INTERFACE                                   | 38     |

| FIGURE 26            | PMC-BISERIAL-III BAE9 FRONT PANEL INTERFACE                           | 39     |

## **Product Description**

The PMC-BiSerial-III BAE9 is part of the PMC Module family of modular I/O products by Dynamic Engineering. It meets the PMC and CMC draft Standards. In standard configuration, the PMC-BiSerial-III BAE9 is a Type 1 mechanical with only low profile passive components on the back of the board, one slot wide, with 10 mm inter-board height. Contact Dynamic Engineering for a copy of this specification. It is assumed that the reader is at least casually familiar with this document and basic logic design.

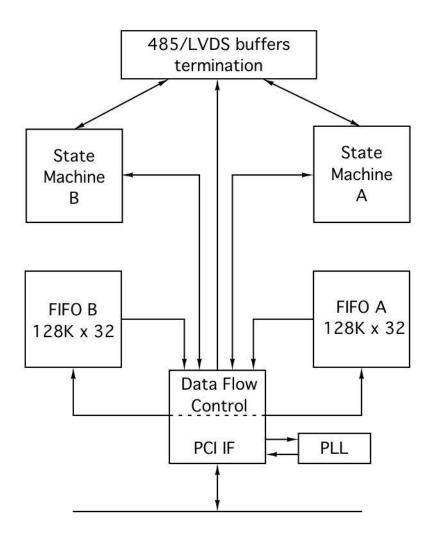

#### FIGURE 1

PMC-BISERIAL-III BLOCK DIAGRAM

The PMC-BiSerial-III is capable of providing multiple serial protocols using either LVDS or RS-485 I/O standards. The PMC-BiSerial-III standard configuration shown in Figure 1 has two optional data FIFOs that can be as large as 128k x 32 bits to accommodate designs requiring a large amount of buffering. In most designs these FIFOs are not installed and internal FIFOs or dual-port RAMs implemented with the block RAM in the Xilinx FPGA are used instead.

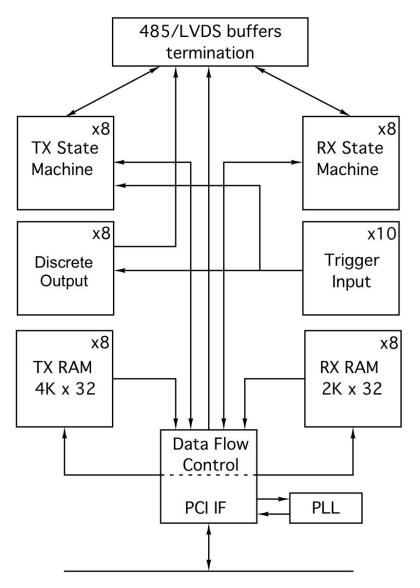

#### FIGURE 2

PMC-BISERIAL-III BAE9 BLOCK DIAGRAM

The PMC-BiSerial-III BAE9 configuration is shown in figure 2. The protocol implemented provides eight I/O channels each with two RS-485 transceivers. The onboard PLL is used to generate two clocks. PLL clock A supplies the clock reference for the asynchronous message interfaces. PLL clock B supplies the clock reference for the discrete output signal and the discrete input trigger signal monitoring functions. The PLL is programmable and uses a 40 MHz reference oscillator to generate a wide range of frequencies. The UART interface can operate at up to 10 M bits/second using a 160 MHz reference clock.

Data for all channels is sent and received LSB first using a low start-bit and one or two high stop-bits to separate data bytes. An optional parity bit following the eight data bits can be configured to implement odd, even, mark (always high), or space (always low) parity. The marking (idle) state of the interface is high. Transmit and receive messages always start on a 32-bit word boundary. Unsent bytes in a 32-bit transmit word are ignored and unpopulated bytes in the last 32-bit received word are filled with zeros.

Each channel can be configured for either half or full-duplex operation. In half-duplex mode, the receiver data is read from the transmit I/O while the transmitter is in a high impedance state. Pull-up / pull-down resistor packs can be installed on the eight transmit I/O lines to suppress glitching when switching directions in half-duplex mode.

Each channel of the BAE9 implementation has a 16 Mbyte RAM for storing message data for the transmit function and an 8 Mbyte RAM for storing received message data. Each RAM's address space is mapped to the PCI bus Base Address Register 1 (BAR1) to allow write and read access to / from individual 32-bit words. In addition, write DMA access to the transmit RAM and read DMA access from the receive RAM is used to move larger data blocks. The starting address offsets for the transmitter and receiver I/O functions are programmable.

The transmitter state-machine reads data-words sequentially from the transmit RAM starting at the stored starting address offset and sends the data LSB first until the bytecount specified is reached. If the transmitter is re-enabled, it will send data starting at that same starting address offset. In order to send different message data, the starting address must be updated or the RAM data re-written. Multiple messages can be initially stored in the transmit RAM and then independently selected by the user by changing the starting address offset for the transmitter.

The receiver state-machine will begin storing received data-words in the next word after the programmed starting address offset. When the message is complete, a statusword which contains the message byte-count and the starting address of the next message will be written to the initial RAM location that was skipped when the message data was written. Unlike the transmitter, the receiver will store subsequent messages in the memory space immediately following the message just received. By reading the status-word of the first message, the address of the status-word for the next message is known. This process can be continued until the address of the message of interest is found. Using the byte count in that message's status-word, a DMA can be setup to quickly read the message data and process accordingly.

Various interrupts are supported by the PMC-BiSerial-III BAE9. An interrupt can be configured to occur at the end of a received or transmitted message. Receiver parity or framing errors are detected and latched, and can also be configured to cause an interrupt. All interrupts can be individually masked, and a master channel interrupt enable is also provided to disable all interrupts for a channel. The current status of interrupt conditions is available even when the interrupt is disabled making it possible to operate in a polled mode. Most configuration registers support read and write operations for maximum software convenience. All addresses are long word (32-bit) aligned.

Potentially thirty-four differential I/O are available at the front bezel for the serial signals. The drivers and receivers conform to the RS-485 specification. The RS-485 signals are selectively terminated with 100 $\Omega$  by software. The termination resistors are in two-element packages to allow flexible termination options for custom formats and protocols. Optional pull-up/pull-down resistor packs can also be installed to provide a logic '1' on undriven lines. In this design 4.7 k $\Omega$  pull-up/pull-down resistors have been installed on the eight transmit lines to prevent erroneous data when switching directions in half-duplex mode.

The PMC-BiSerial-III BAE9 design uses all 34 I/O lines. Sixteen for the UARTs (one in and one out for each of the eight channels), eight for the discrete output signals (one per channel) and ten discrete input signals any one of which can be selected on a per channel basis.

Other custom interfaces are available on request. We will redesign the state machines and create a custom interface protocol that meets your requirements. That protocol will then be offered as a "standard" special order product. Please see our web page for current protocols offered. If none of these fulfill your needs, contact Dynamic Engineering with your custom application.

Since the PMC-BiSerial-III BAE9 conforms to the PMC and CMC draft standards, it is guaranteed to be compatibile with multiple PMC Carrier boards. Because the PMC may be mounted on different form factors, while maintaining plug and software compatibility, system prototyping may be done on one PMC Carrier board, while final system implementation uses a different one.

The PMC-BiSerial-III BAE9 uses a 10 mm inter-board spacing for the front panel, standoffs, and PMC connectors. The 10 mm height is the "standard" height and will work in most systems with most carriers. If your carrier has non-standard connectors (height) to mate with the PMC-BiSerial-III BAE9, please let us know. We may be able to do a special build with a different height connector to compensate.

## **Theory of Operation**

The PMC-BiSerial-III BAE9 features an XC3S4000-5 Spartan 3 Xilinx FPGA. The FPGA contains all of the registers, dual-port RAMs and protocol controlling elements of the PMC-BiSerial-III BAE9 design. Only the transceivers, switches and PLL circuit are external to the Xilinx device.

A logic block within the Xilinx controls the PCI interface to the host CPU. The PMC-BiSerial-III BAE9 requires one wait state for read / write cycles to any address. The wait states refer to the number of clocks after the PCI core decodes the address and control signals and before the "terminate with data" state is reached. Two additional clock periods account for the delay to decode the signals from the PCI bus and to convert the terminate-with-data state into the TRDY signal.

Scatter-gather DMA is supported in this design with the memory page information stored in host RAM as a series of chaining descriptors. Once the physical address of the first chaining descriptor is written to the appropriate DMA pointer register, the interface will read a 16-byte block from this location. The first four bytes comprise a long-word indicating the physical address of the first block of the I/O buffer passed to the read or write call. The next four bytes specify the address offset in the corresponding local RAM that is the target of the data transfer. The next four bytes are a long-word indicating the physical address of the next chaining descriptor along with two flag bits, in bit position 0 and 1. Bit zero is set to a '1' if this descriptor is the last in the chain. Bit one is set to a '1' if the I/O transfer is from the PMC-BiSerial-III BAE9 board to host memory, and a '0' if the transfer is from memory to the board. These bits are then replaced with zeros to determine the address of the next descriptor, if there is one.

Transmitting data requires a number of steps to be performed. The PLL must be programmed to supply the I/O clock. The message data must be written to the TX RAM, the starting address of the message stored and the transmitter configuration specified. Finally, the transmitter must be enabled along with the number of bytes to be sent. These steps do not need to be performed in this order, but they must all be done to accomplish the transfer. The least significant byte of the RAM word is sent first then the next significant byte follows until the entire 32-bit word is sent. If a byte count is requested that is not divisible by four, the remaining bytes of the last RAM word are discarded and a subsequent transmission will begin with a new 32-bit word. The transmitter can operate in one of four modes: triggered, where the transmitter waits for a trigger signal to be seen then waits for a programmable delay count to expire before sending the requested message; periodic, where the message is sent immediately and thereafter once for each time a programmable period count is reached; one-shot, where the message is sent immediately only once; and triggered periodic, which initially behaves like the triggered mode, but then repeats the message like the periodic mode. Multiple messages can be pre-written to the transmit RAM and then randomly selected by the user by rewriting the starting I/O address.

In order to receive data it is only necessary to configure the PLL, configure and enable the receiver and wait for data to be received. A 16-bit counter is incremented for each data byte received. Once the reception has started, a 32-bit data word will be stored in the receive RAM for each four bytes received. The first byte is stored in the least significant byte of the RAM word and each subsequent byte is stored in the next most significant byte. When the input data line is idle for at least eight bit-periods the reception will terminate. This will cause the received byte count to be written to the byte count register, the message status-word to be written to RAM at the beginning of the message memory space and the receiver done status bit set. If the last RAM word was not completely filled, the last partial word will be written to the receiver enable bit will be cleared, otherwise the receiver will remain enabled and will wait for the next start-bit to continue receiving data.

Each channel also has a discrete output signal that can be configured to operate in the same four modes as the transmit UART. The signal is a pulse that is determined by the programmable period and duty counts. PLL clock B supplies the timing reference for these counts. The polarity of the signal output and the trigger input, as well as the trigger input for the transmit UART, can be selected by control bits in the transmit control register.

Additionally there are ten RS-485 I/O lines used for discrete input signals used as triggers by the transmit UART or discrete output signals. Each channel can select one of these ten lines without restriction (any or all channels can select the same line). A trigger monitor function counts the duration of the trigger high and low logic levels. Four latched status bits are set if the high or low logic levels exceed minimum or maximum programmable time counts. The counts of the last high and low level pulse are stored and are available to be read. In rev. D these count fields were expanded from sixteen to twenty-two bits and in rev E the ability to detect a steady-state signal was added. PLL clock B is used as a timing reference for these functions.

The baud-rate of the UART interface can be programmed to one of 48 values without changing the PLL clock A frequency. These values represent a four-to-one ratio and each channel's baud-rate can be adjusted independently. Typically, the receive UART uses a 16x clock to decode the asynchronous data-stream since the sender and receiver may be operating at slightly different clock rates. To allow the receiver to operate over a wider frequency range, we divide the bit period into three sections. During the beginning section, if a data transition is seen, the bit-time counter will reset as it assumes this is the beginning of a new data-bit. The middle of the middle section will again be looking for a data transition, and if seen will reset the bit-time counter and move to the beginning section of the next bit. The count values that mark the limits of these three sections are modified based on the clocks per bit-period setting which is programmable from 16 to 64 clocks per bit.

The values of the transition counts for each bit-width value and the resulting baud-rates (based on a PLL clock A frequency of 160 MHz) are listed below.

| 0x0F         16         10.000 Mbps         2         7         13         15           0x10         17         9.412 Mbps         3         8         13         16           0x11         18         8.899 Mbps         3         9         15         18           0x13         20         8.000 Mbps         3         9         16         19           0x14         21         7.619 Mbps         3         10         17         20           0x15         22         7.273 Mbps         3         11         19         22           0x17         24         6.667 Mbps         3         11         20         23           0x18         25         6.400 Mbps         4         12         20         24           0x19         26         6.154 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         24         28           0x1C         29         5.517 Mbps         5         17         30         35           0x20                                                                                                      | <u>Register</u> | Divide | Baud Rate   | low | mid | high | end |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--------|-------------|-----|-----|------|-----|

| 0x11         18         8.889 Mbps         3         8         14         17           0x12         19         8.421 Mbps         3         9         15         18           0x13         20         8.000 Mbps         3         9         16         19           0x14         21         7.619 Mbps         3         10         17         20           0x15         22         7.273 Mbps         3         11         19         22           0x17         24         6.667 Mbps         3         11         20         23           0x18         25         6.400 Mbps         4         12         21         25           0x1A         27         5.926 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         15         26         30           0x1F         32         5.000 Mbps         4         15         27         31           0x20                                                                                                      | 0x0F            |        | 10.000 Mbps |     | 7   |      | 15  |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0x10            | 17     | 9.412 Mbps  |     | 8   | 13   | 16  |

| 0x13         20         8.000 Mbps         3         9         16         19           0x14         21         7.619 Mbps         3         10         17         20           0x15         22         7.273 Mbps         3         11         19         22           0x17         24         6.667 Mbps         3         11         20         23           0x18         25         6.400 Mbps         4         12         20         24           0x19         26         6.154 Mbps         4         13         22         26           0x1A         27         5.926 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         25         29           0x1F         32         5.000 Mbps         4         15         26         30           0x21         34         4.706 Mbps         5         16         28         33           0x22         35         4.571 Mbps         5         18         32         37           0x23 <td>0x11</td> <td>18</td> <td>8.889 Mbps</td> <td></td> <td>8</td> <td>14</td> <td>17</td>         | 0x11            | 18     | 8.889 Mbps  |     | 8   | 14   | 17  |

| 0x14         21         7.619 Mbps         3         10         17         20           0x15         22         7.273 Mbps         3         10         18         21           0x16         23         6.957 Mbps         3         11         19         22           0x17         24         6.667 Mbps         3         11         20         23           0x18         25         6.400 Mbps         4         12         21         25           0x1A         27         5.926 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         25         29           0x1E         31         5.161 Mbps         5         16         27         31           0x20         33         4.848 Mbps         5         16         28         33           0x21         34         4.706 Mbps         5         17         30         35           0x223         36         4.444 Mbps         5         17         30         35           0x24 </td <td>0x12</td> <td>19</td> <td>8.421 Mbps</td> <td>3</td> <td>9</td> <td>15</td> <td>18</td> | 0x12            | 19     | 8.421 Mbps  | 3   | 9   | 15   | 18  |

| 0x14         21         7.619 Mbps         3         10         17         20           0x15         22         7.273 Mbps         3         10         18         21           0x16         23         6.957 Mbps         3         11         19         22           0x17         24         6.667 Mbps         3         11         20         23           0x18         25         6.400 Mbps         4         12         21         25           0x1A         27         5.926 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         25         29           0x1E         31         5.161 Mbps         5         16         27         31           0x20         33         4.848 Mbps         5         16         28         33           0x21         34         4.706 Mbps         5         17         30         35           0x223         36         4.444 Mbps         5         17         30         35           0x24 </td <td>0x13</td> <td>20</td> <td>8.000 Mbps</td> <td></td> <td>9</td> <td>16</td> <td>19</td>  | 0x13            | 20     | 8.000 Mbps  |     | 9   | 16   | 19  |

| 0x15         22         7.273 Mbps         3         10         18         21           0x16         23         6.957 Mbps         3         11         19         22           0x17         24         6.667 Mbps         3         11         20         23           0x18         25         6.400 Mbps         4         12         20         24           0x19         26         6.154 Mbps         4         13         22         26           0x1A         27         5.926 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         15         26         30           0x1F         31         5.161 Mbps         4         15         27         31           0x20         33         4.848 Mbps         5         16         27         32           0x21         34         4.706 Mbps         5         18         31         36           0x22         35         4.571 Mbps         5         18         32         37           0x23 <td>0x14</td> <td>21</td> <td>7.619 Mbps</td> <td></td> <td>10</td> <td>17</td> <td>20</td>       | 0x14            | 21     | 7.619 Mbps  |     | 10  | 17   | 20  |

| 0x16         23         6.957 Mbps         3         11         19         22           0x17         24         6.667 Mbps         3         11         20         23           0x18         25         6.400 Mbps         4         12         20         24           0x19         26         6.154 Mbps         4         12         21         25           0x1A         27         5.926 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         25         29           0x1E         31         5.161 Mbps         4         15         26         30           0x1F         32         5.000 Mbps         4         15         27         31           0x20         33         4.848 Mbps         5         16         28         33           0x21         34         4.706 Mbps         5         18         31         36           0x223         36         4.414 Mbps         5         18         32         37           0x24 </td <td></td> <td>22</td> <td></td> <td></td> <td></td> <td>18</td> <td></td>                   |                 | 22     |             |     |     | 18   |     |

| 0x17         24         6.667 Mbps         3         11         20         23           0x18         25         6.400 Mbps         4         12         20         24           0x19         26         6.154 Mbps         4         12         21         25           0x1A         27         5.926 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         25         29           0x1E         31         5.161 Mbps         4         15         26         30           0x1F         32         5.000 Mbps         4         15         27         31           0x20         33         4.848 Mbps         5         16         28         33           0x22         35         4.571 Mbps         5         17         30         35           0x23         36         4.444 Mbps         5         18         31         36           0x24         37         4.324 Mbps         5         18         31         36           0x26 <td></td> <td>23</td> <td></td> <td>3</td> <td></td> <td></td> <td></td>                          |                 | 23     |             | 3   |     |      |     |

| 0x18         25         6.400 Mbps         4         12         20         24           0x19         26         6.154 Mbps         4         12         21         25           0x1A         27         5.926 Mbps         4         13         22         26           0x1B         28         5.714 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         25         29           0x1E         31         5.161 Mbps         4         15         26         30           0x1F         32         5.000 Mbps         4         15         27         31           0x20         33         4.848 Mbps         5         16         27         32           0x21         34         4.706 Mbps         5         17         30         35           0x23         36         4.444 Mbps         5         17         30         35           0x24         37         4.324 Mbps         5         18         31         36           0x24 <td></td> <td></td> <td>•</td> <td></td> <td></td> <td></td> <td></td>                            |                 |        | •           |     |     |      |     |

| 0x19         26         6.154 Mbps         4         12         21         25           0x1A         27         5.926 Mbps         4         13         22         26           0x1B         28         5.714 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         25         29           0x1E         31         5.161 Mbps         4         15         27         31           0x20         33         4.848 Mbps         5         16         27         32           0x21         34         4.706 Mbps         5         17         29         34           0x23         36         4.444 Mbps         5         17         30         35           0x24         37         4.324 Mbps         5         18         31         36           0x27         40         4.000 Mbps         5         19         33         38           0x27         40         4.000 Mbps         6         20         35         41           0x28 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                             |                 |        |             |     |     |      |     |

| 0x1A         27         5.926 Mbps         4         13         22         26           0x1B         28         5.714 Mbps         4         13         23         27           0x1C         29         5.517 Mbps         4         14         24         28           0x1D         30         5.333 Mbps         4         14         25         29           0x1E         31         5.161 Mbps         4         15         27         31           0x20         33         4.848 Mbps         5         16         28         33           0x21         34         4.706 Mbps         5         16         28         33           0x22         35         4.571 Mbps         5         17         29         34           0x23         36         4.444 Mbps         5         17         30         35           0x24         37         4.324 Mbps         5         18         31         36           0x25         38         4.211 Mbps         5         19         33         38           0x27         40         4.000 Mbps         6         20         35         41           0x28 <td></td> <td></td> <td>•</td> <td></td> <td></td> <td></td> <td></td>                            |                 |        | •           |     |     |      |     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        |             |     |     |      |     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        |             |     |     |      |     |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 |        | •           |     |     |      |     |

| 0x1E315.161 Mbps4152630 $0x1F$ 325.000 Mbps4152731 $0x20$ 334.848 Mbps5162732 $0x21$ 344.706 Mbps5162833 $0x22$ 354.571 Mbps5172934 $0x23$ 364.444 Mbps5173035 $0x24$ 374.324 Mbps5183136 $0x25$ 384.211 Mbps5183237 $0x26$ 394.103 Mbps5193338 $0x27$ 404.000 Mbps5193439 $0x28$ 413.902 Mbps6203541 $0x29$ 423.810 Mbps6213642 $0x24$ 33.721 Mbps6213743 $0x2C$ 453.556 Mbps6223844 $0x2D$ 463.478 Mbps6234046 $0x2F$ 483.333 Mbps6234147 $0x30$ 493.265 Mbps7244148 $0x31$ 503.200 Mbps7254350 $0x34$ 533.019 Mbps7264552 $0x35$ 542.963 Mbps7274754 $0x36$ 552.909 Mbps7274855<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |        |             |     |     |      |     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        |             |     |     |      |     |

| 0x20 $33$ $4.848$ Mbps $5$ $16$ $27$ $32$ $0x21$ $34$ $4.706$ Mbps $5$ $16$ $28$ $33$ $0x22$ $35$ $4.571$ Mbps $5$ $17$ $29$ $34$ $0x23$ $36$ $4.444$ Mbps $5$ $17$ $30$ $35$ $0x24$ $37$ $4.324$ Mbps $5$ $18$ $31$ $36$ $0x25$ $38$ $4.211$ Mbps $5$ $18$ $32$ $37$ $0x26$ $39$ $4.103$ Mbps $5$ $19$ $33$ $38$ $0x27$ $40$ $4.000$ Mbps $5$ $19$ $34$ $39$ $0x28$ $41$ $3.902$ Mbps $6$ $20$ $34$ $40$ $0x29$ $42$ $3.810$ Mbps $6$ $20$ $35$ $41$ $0x24$ $43$ $3.721$ Mbps $6$ $21$ $36$ $42$ $0x2B$ $44$ $3.636$ Mbps $6$ $21$ $37$ $43$ $0x2C$ $45$ $3.556$ Mbps $6$ $22$ $38$ $44$ $0x2D$ $46$ $3.478$ Mbps $6$ $23$ $40$ $46$ $0x2F$ $48$ $3.333$ Mbps $6$ $23$ $41$ $47$ $0x30$ $49$ $3.265$ Mbps $7$ $24$ $41$ $48$ $0x31$ $50$ $3.0077$ Mbps $7$ $25$ $43$ $50$ $0x34$ $53$ $3.019$ Mbps $7$ $26$ $45$ $52$ $0x35$ $54$ $2.963$ Mbps $7$ $27$ <                                                                                                                                                                                                                                                                                                                                             |                 |        |             |     |     |      |     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        |             |     |     |      |     |

| 0x22 $35$ $4.571$ Mbps $5$ $17$ $29$ $34$ $0x23$ $36$ $4.444$ Mbps $5$ $17$ $30$ $35$ $0x24$ $37$ $4.324$ Mbps $5$ $18$ $31$ $36$ $0x25$ $38$ $4.211$ Mbps $5$ $18$ $32$ $37$ $0x26$ $39$ $4.103$ Mbps $5$ $19$ $33$ $38$ $0x27$ $40$ $4.000$ Mbps $5$ $19$ $34$ $39$ $0x28$ $41$ $3.902$ Mbps $6$ $20$ $34$ $40$ $0x29$ $42$ $3.810$ Mbps $6$ $20$ $35$ $41$ $0x24$ $43$ $3.721$ Mbps $6$ $21$ $36$ $42$ $0x28$ $44$ $3.636$ Mbps $6$ $21$ $37$ $43$ $0x2C$ $45$ $3.556$ Mbps $6$ $22$ $38$ $44$ $0x2D$ $46$ $3.478$ Mbps $6$ $23$ $40$ $46$ $0x2E$ $47$ $3.404$ Mbps $6$ $23$ $41$ $47$ $0x30$ $49$ $3.265$ Mbps $7$ $24$ $42$ $49$ $0x32$ $51$ $3.137$ Mbps $7$ $25$ $43$ $50$ $0x33$ $52$ $3.077$ Mbps $7$ $26$ $46$ $53$ $0x34$ $53$ $3.019$ Mbps $7$ $27$ $47$ $54$ $0x33$ $52$ $3.077$ Mbps $7$ $26$ $46$ $53$ $0x34$ $53$ $3.019$ Mbps $7$ $27$ </td <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                                                                                                                                                                                                                                                                     |                 |        |             |     |     |      |     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        |             |     |     |      |     |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        |             |     |     |      |     |

| 0x25         38         4.211 Mbps         5         18         32         37           0x26         39         4.103 Mbps         5         19         33         38           0x27         40         4.000 Mbps         5         19         34         39           0x28         41         3.902 Mbps         6         20         34         40           0x29         42         3.810 Mbps         6         21         36         42           0x2A         43         3.721 Mbps         6         21         37         43           0x2C         45         3.556 Mbps         6         22         38         44           0x2D         46         3.478 Mbps         6         22         39         45           0x2E         47         3.404 Mbps         6         23         40         46           0x2F         48         3.333 Mbps         7         24         41         48           0x31         50         3.200 Mbps         7         24         42         49           0x32         51         3.137 Mbps         7         25         43         50           0x33 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                             |                 |        |             |     |     |      |     |

| 0x26394.103 Mbps51933380x27404.000 Mbps51934390x28413.902 Mbps62034400x29423.810 Mbps62035410x2A433.721 Mbps62136420x2B443.636 Mbps62137430x2C453.556 Mbps62238440x2D463.478 Mbps62340460x2F483.333 Mbps62341470x30493.265 Mbps72441480x31503.200 Mbps72442490x32513.137 Mbps72543500x33523.019 Mbps72645520x35542.963 Mbps72748550x38572.807 Mbps72748550x38572.807 Mbps82848560x39582.759 Mbps82849570x3A592.712 Mbps82950580x3B602.667 Mbps82951590x3C612.623 Mbps83053610x3D622.581 Mbps83053610x3E632.540 Mbps<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        |             |     |     |      |     |

| 0x27         40         4.000 Mbps         5         19         34         39           0x28         41         3.902 Mbps         6         20         34         40           0x29         42         3.810 Mbps         6         20         35         41           0x2A         43         3.721 Mbps         6         21         36         42           0x2B         44         3.636 Mbps         6         21         37         43           0x2C         45         3.556 Mbps         6         22         38         44           0x2D         46         3.478 Mbps         6         23         40         46           0x2E         47         3.404 Mbps         6         23         41         47           0x30         49         3.265 Mbps         7         24         41         48           0x31         50         3.200 Mbps         7         25         43         50           0x33         52         3.077 Mbps         7         25         44         51           0x34         53         3.019 Mbps         7         26         45         52           0x35 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                             |                 |        |             |     |     |      |     |

| 0x28413.902 Mbps62034400x29423.810 Mbps62035410x2A433.721 Mbps62136420x2B443.636 Mbps62137430x2C453.556 Mbps62238440x2D463.478 Mbps62239450x2E473.404 Mbps62340460x2F483.333 Mbps62341470x30493.265 Mbps72441480x31503.200 Mbps72442490x32513.137 Mbps72543500x33523.077 Mbps72645520x34533.019 Mbps72646530x36552.909 Mbps72747540x37562.857 Mbps72748550x38572.807 Mbps82849570x3A592.712 Mbps82950580x3B602.667 Mbps82951590x3C612.623 Mbps83053610x3D622.581 Mbps83053610x3E632.540 Mbps8315462                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |        |             |     |     |      |     |

| 0x29         42         3.810 Mbps         6         20         35         41           0x2A         43         3.721 Mbps         6         21         36         42           0x2B         44         3.636 Mbps         6         21         37         43           0x2C         45         3.556 Mbps         6         22         38         44           0x2D         46         3.478 Mbps         6         22         39         45           0x2E         47         3.404 Mbps         6         23         40         46           0x2F         48         3.333 Mbps         6         23         41         47           0x30         49         3.265 Mbps         7         24         41         48           0x31         50         3.200 Mbps         7         25         43         50           0x32         51         3.137 Mbps         7         25         44         51           0x34         53         3.019 Mbps         7         26         45         52           0x35         54         2.963 Mbps         7         26         46         53           0x36 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                             |                 |        |             |     |     |      |     |

| 0x2A       43       3.721 Mbps       6       21       36       42         0x2B       44       3.636 Mbps       6       21       37       43         0x2C       45       3.556 Mbps       6       22       38       44         0x2D       46       3.478 Mbps       6       22       39       45         0x2E       47       3.404 Mbps       6       23       40       46         0x2F       48       3.333 Mbps       6       23       41       47         0x30       49       3.265 Mbps       7       24       41       48         0x31       50       3.200 Mbps       7       24       42       49         0x32       51       3.137 Mbps       7       25       43       50         0x33       52       3.077 Mbps       7       26       45       52         0x34       53       3.019 Mbps       7       26       45       52         0x35       54       2.963 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38                                                                                                                                                                                                 |                 |        |             |     |     |      |     |

| 0x2B       44       3.636 Mbps       6       21       37       43         0x2C       45       3.556 Mbps       6       22       38       44         0x2D       46       3.478 Mbps       6       22       39       45         0x2E       47       3.404 Mbps       6       23       40       46         0x2F       48       3.333 Mbps       6       23       41       47         0x30       49       3.265 Mbps       7       24       41       48         0x31       50       3.200 Mbps       7       25       43       50         0x32       51       3.137 Mbps       7       25       44       51         0x33       52       3.077 Mbps       7       26       45       52         0x34       53       3.019 Mbps       7       26       45       52         0x35       54       2.963 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38       57       2.807 Mbps       8       28       49       57         0x38                                                                                                                                                                                                 |                 |        |             |     |     |      |     |

| 0x2C       45       3.556 Mbps       6       22       38       44         0x2D       46       3.478 Mbps       6       22       39       45         0x2E       47       3.404 Mbps       6       23       40       46         0x2F       48       3.333 Mbps       6       23       41       47         0x30       49       3.265 Mbps       7       24       41       48         0x31       50       3.200 Mbps       7       24       42       49         0x32       51       3.137 Mbps       7       25       43       50         0x33       52       3.077 Mbps       7       26       45       52         0x33       52       3.019 Mbps       7       26       45       52         0x34       53       3.019 Mbps       7       26       46       53         0x36       55       2.909 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38       57       2.807 Mbps       8       28       49       57         0x38                                                                                                                                                                                                 |                 |        |             |     |     |      |     |

| 0x2D         46         3.478 Mbps         6         22         39         45           0x2E         47         3.404 Mbps         6         23         40         46           0x2F         48         3.333 Mbps         6         23         41         47           0x30         49         3.265 Mbps         7         24         41         48           0x31         50         3.200 Mbps         7         24         42         49           0x32         51         3.137 Mbps         7         25         43         50           0x33         52         3.077 Mbps         7         26         45         52           0x34         53         3.019 Mbps         7         26         46         53           0x36         55         2.909 Mbps         7         27         47         54           0x37         56         2.857 Mbps         7         27         48         55           0x38         57         2.807 Mbps         8         28         49         57           0x38         57         2.807 Mbps         8         29         50         58           0x39 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td>                             |                 |        |             |     |     |      |     |

| 0x2E       47       3.404 Mbps       6       23       40       46         0x2F       48       3.333 Mbps       6       23       41       47         0x30       49       3.265 Mbps       7       24       41       48         0x31       50       3.200 Mbps       7       24       42       49         0x32       51       3.137 Mbps       7       25       43       50         0x33       52       3.077 Mbps       7       26       45       52         0x34       53       3.019 Mbps       7       26       46       53         0x34       53       3.019 Mbps       7       26       46       53         0x35       54       2.963 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38       57       2.807 Mbps       8       28       48       56         0x39       58       2.759 Mbps       8       28       49       57         0x3A       59       2.712 Mbps       8       29       50       58         0x3B                                                                                                                                                                                                 |                 |        |             |     |     |      |     |

| 0x2F       48       3.333 Mbps       6       23       41       47         0x30       49       3.265 Mbps       7       24       41       48         0x31       50       3.200 Mbps       7       24       42       49         0x32       51       3.137 Mbps       7       25       43       50         0x33       52       3.077 Mbps       7       25       44       51         0x34       53       3.019 Mbps       7       26       45       52         0x35       54       2.963 Mbps       7       26       46       53         0x36       55       2.909 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38       57       2.807 Mbps       8       28       48       56         0x39       58       2.759 Mbps       8       28       49       57         0x3A       59       2.712 Mbps       8       29       50       58         0x3B       60       2.667 Mbps       8       30       52       60         0x3D                                                                                                                                                                                                 |                 |        |             |     |     |      |     |

| 0x30       49       3.265 Mbps       7       24       41       48         0x31       50       3.200 Mbps       7       24       42       49         0x32       51       3.137 Mbps       7       25       43       50         0x33       52       3.077 Mbps       7       25       44       51         0x34       53       3.019 Mbps       7       26       45       52         0x35       54       2.963 Mbps       7       26       46       53         0x36       55       2.909 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38       57       2.807 Mbps       8       28       49       57         0x38       57       2.807 Mbps       8       28       49       57         0x38       57       2.807 Mbps       8       28       49       57         0x38       57       2.807 Mbps       8       29       50       58         0x39       58       2.759 Mbps       8       29       50       58         0x3C                                                                                                                                                                                                 |                 |        |             |     |     |      |     |

| 0x31       50       3.200 Mbps       7       24       42       49         0x32       51       3.137 Mbps       7       25       43       50         0x33       52       3.077 Mbps       7       25       44       51         0x34       53       3.019 Mbps       7       26       45       52         0x35       54       2.963 Mbps       7       26       46       53         0x36       55       2.909 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38       57       2.807 Mbps       8       28       49       57         0x38       57       2.807 Mbps       8       29       50       58         0x39       58       2.759 Mbps       8       29       50       58         0x3C                                                                                                                                                                                                 |                 |        |             |     |     |      |     |

| 0x32       51       3.137 Mbps       7       25       43       50         0x33       52       3.077 Mbps       7       25       44       51         0x34       53       3.019 Mbps       7       26       45       52         0x35       54       2.963 Mbps       7       26       46       53         0x36       55       2.909 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38       57       2.807 Mbps       8       28       48       56         0x39       58       2.759 Mbps       8       28       49       57         0x3A       59       2.712 Mbps       8       29       50       58         0x3B       60       2.667 Mbps       8       29       51       59         0x3C       61       2.623 Mbps       8       30       52       60         0x3D       62       2.581 Mbps       8       30       53       61         0x3E       63       2.540 Mbps       8       31       54       62                                                                                                                                                                                                              |                 |        |             |     |     |      |     |

| 0x33523.077 Mbps72544510x34533.019 Mbps72645520x35542.963 Mbps72646530x36552.909 Mbps72747540x37562.857 Mbps72748550x38572.807 Mbps82848560x39582.759 Mbps82849570x3A592.712 Mbps82950580x3B602.667 Mbps82951590x3C612.623 Mbps83052600x3D622.581 Mbps83053610x3E632.540 Mbps8315462                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |        | •           |     |     |      |     |

| 0x34533.019 Mbps72645520x35542.963 Mbps72646530x36552.909 Mbps72747540x37562.857 Mbps72748550x38572.807 Mbps82848560x39582.759 Mbps82849570x3A592.712 Mbps82950580x3B602.667 Mbps82951590x3C612.623 Mbps83052600x3D622.581 Mbps83053610x3E632.540 Mbps8315462                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |        |             |     |     |      |     |

| 0x35542.963 Mbps72646530x36552.909 Mbps72747540x37562.857 Mbps72748550x38572.807 Mbps82848560x39582.759 Mbps82849570x3A592.712 Mbps82950580x3B602.667 Mbps82951590x3C612.623 Mbps83052600x3D622.581 Mbps83053610x3E632.540 Mbps8315462                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |        |             |     |     |      |     |

| 0x36       55       2.909 Mbps       7       27       47       54         0x37       56       2.857 Mbps       7       27       48       55         0x38       57       2.807 Mbps       8       28       48       56         0x39       58       2.759 Mbps       8       28       49       57         0x3A       59       2.712 Mbps       8       29       50       58         0x3B       60       2.667 Mbps       8       29       51       59         0x3C       61       2.623 Mbps       8       30       52       60         0x3D       62       2.581 Mbps       8       30       53       61         0x3E       63       2.540 Mbps       8       31       54       62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                 |        |             |     |     |      |     |

| 0x37562.857 Mbps72748550x38572.807 Mbps82848560x39582.759 Mbps82849570x3A592.712 Mbps82950580x3B602.667 Mbps82951590x3C612.623 Mbps83052600x3D622.581 Mbps83053610x3E632.540 Mbps8315462                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 |        |             |     |     |      |     |