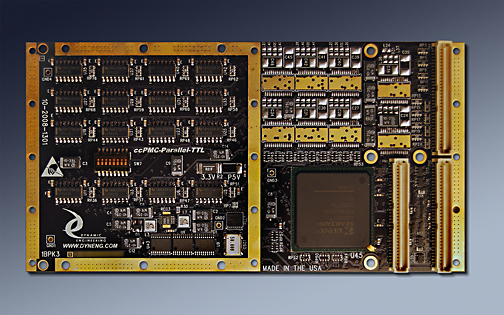

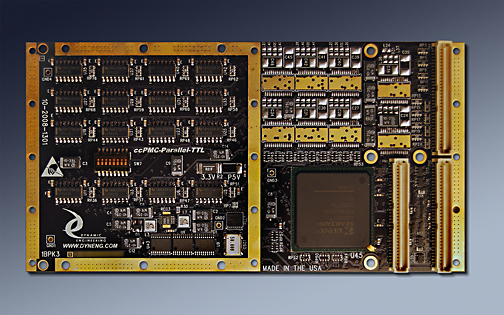

ccPMC-Parallel-TTL

Conduction Cooled PMC Format

Pictured built with TTL option

| Single wide PMC. |

|

| |

|

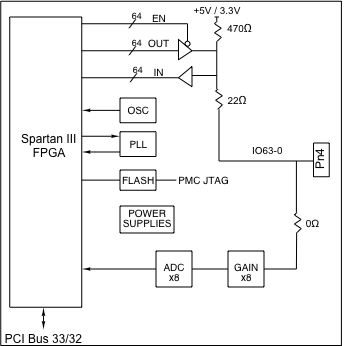

| 64 independent TTL IO. The pull-ups can be referenced to 3.3V or 5V. Rear IO [Pn4] Unused ports isolated with resistors for "zero bus stub". Matched IO within 1/1000 inch for on-board traces. |

|

| |

|

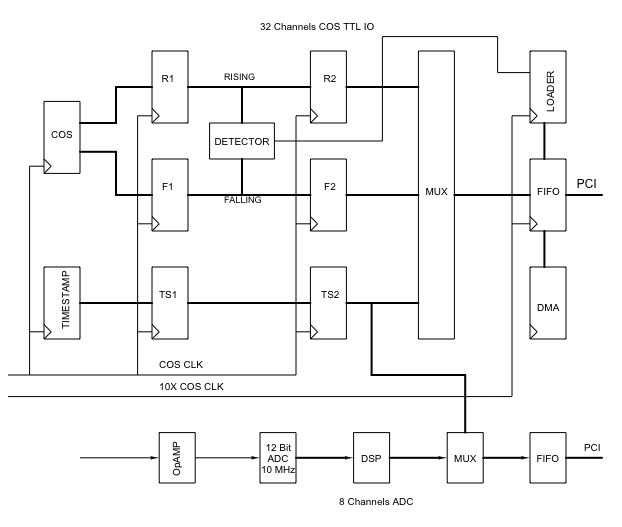

| 8 independent / sychnonized ADC. 12 bit 10 MHz capable ADC´s with opamp buffers and voltage dividers. FIFO support with DMA for each channel. Signal Processing on received data or straight packed data. |

|

| |

|

| 470 standard, 1K, 4.7K available. Double pull-ups available on digital lines |

|

| |

|

| 64+ mA per channel on digital lines |

|

| |

|

| Pn4 backplane connection. Your PMC carrier will specify the system connector. |

|

| |

|

| 32 bit registers mapped to the 64 IO channels. Read-back of channel control registers and input registers. Read-write of control registers for card configuration. Direct and DMA read of ADC data. |

|

| |

|

| All IO Channels can be programmed to cause interrupts. Each channel is programmable to be masked, rising, falling, both [COS]. Level interrupts plus DMA completion on ADC channels. Interrupts are mapped to INTA on PCI bus. |

|

| |

|

| +3V, +5V, and +/- 12V when ADC´s are installed. |

|

| |

|

| The isolation resistor standard is 22 ohms to Pn4. Resisive coupling for current limiting and ESD protection. Other values are available. |

|

| |

|

| Input registers are programmable to capture data with the COS clk. SW can select PLL or Oscillator as the source for clock. A programmable divider allows a wide range of sampling frequencies to be selected. |

|

| All bits are routed through the FPGA to allow for custom state-machine implementations. FIFO and Dual Port RAM can be implemented. See custom models below. |

| ccPMC-Parallel-TTL is a software controlled HW interface. As fast as the PCI interface can push the data across, the outputs can change. With the Windows® driver several accesses per microsecond can be achieved. Your time to market will be shortened by the easy to use interface, flexibility in design, and off-the-shelf availability. With DMA enabled and FIFO´s instantiated faster transfers can occur. Up to 48K x 32 internal FIFO can be achieved with the 4000 sized FPGA. |

|

| |

|

| ccPMC-Parallel-TTL has an attractive price, and low integration cost for a low system cost. ccPMC-Parallel-TTL has an associated PIM and PIM Carrier which can lead to further savings in cPCI environments. |

|

| |

|

| ccPMC-Parallel-TTL is easy to use. A point and shoot user interface to the IO. Please download the manual and see for yourself. The engineering kit provides a good starting point for a new user. |

|

| |

|

| ccPMC-Parallel-TTL is designed to be customized. The base version is available from stock. New "clientized" versions can be dialed in quickly. We can ship a model that is " just like but different" to you right away and follow-up with new FLASH files to match your requirements. You can make a quick start having the HW available right away and adding features as they are available. |

|

| |

|

| ccPMC-Parallel-TTL is a standard single wide PMC [single slot] board which conforms to the PMC mechanical and electrical specifications. Eliminate mechanical interference issues. |

|

| |

|

| ccPMC-Parallel-TTL is PMC compliant per the IEEE 1386 specification. ccPMC-Parallel-TTL is also compliant with the conduction cooled PMC specification. | |

| |

|

| ccPMC-Parallel-TTL is PCI compliant. You can develop with a PCI to PMC adapter - PCI2PMC or PCIBPMC etc.. |