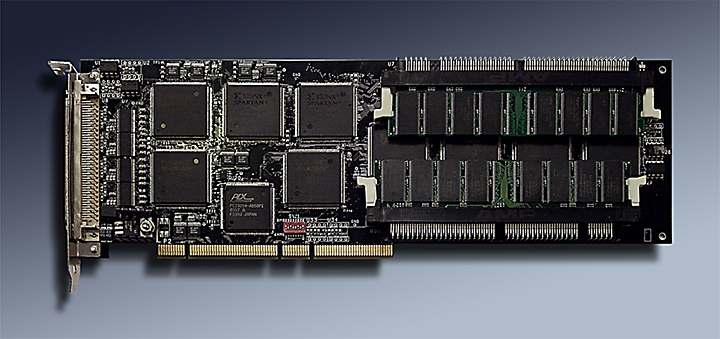

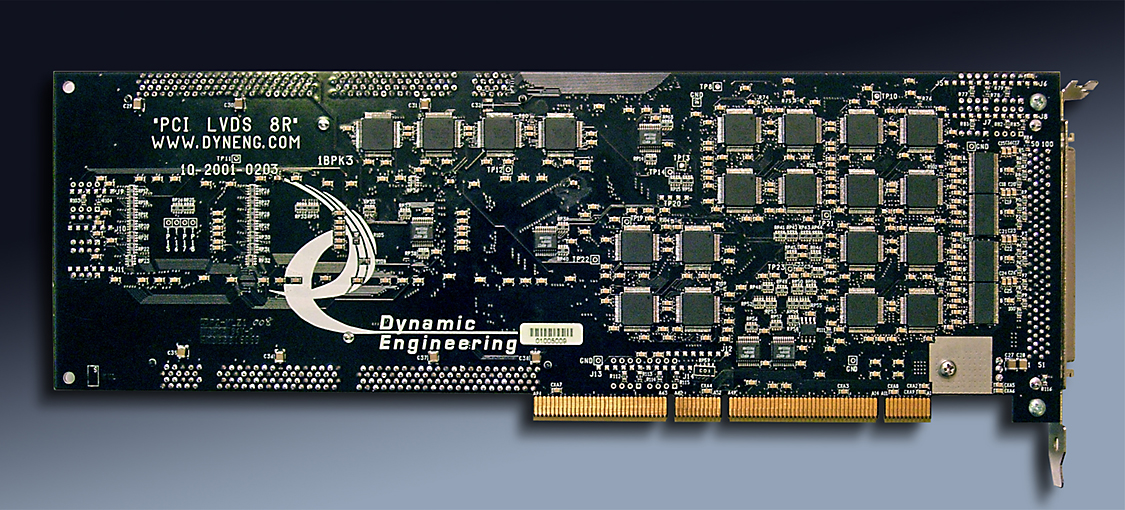

PCI-LVDS-8R

PCI card with 8 channels of LVDS input, digital filtering, and storage

PCI-LVDS-8R Description

- 8 channels TIA/EIA-644 LVDS standard input, Camera Link.

- 2x4 channel configurations

- 2x256 MB SDRAM storage

- Scatter - gather DMA

- Independent clocking on output channels.

- Independent FIFO storage per channel.

- Flexible direct, transmit, and store modes of operation.

- Programmable input data filter.

- Default configuration is to draw board power from the 3.3V power rails.

- 5V configuration is available

- 1 year warranty standard. Extended warranty available.

- Extended [Industrial] Temperature standard.

- ROHS and Standard processing available

PCI-LVDS-8R was designed in 2001. This webpage is provided for reference purposes. If you like the concept and want to purchase we can update the design to be manufacturable with current parts etc. plus support for modern OS. We can also enhance the design to make use of the newer FPGAs and DDR. In addition, PCIe-AlteraCycloneIV is available with PCIe-Spartan-VI due for release. Please contact Dynamic Engineering for more information.

PCI-LVDS-8R is a PCI card with 8 channels. Each channel has memory, processing, and LVDS serialized input. The input is compatible with the TIA/EIA-644 LVDS standard. The serialized data is received with parallel serial data streams plus a reference clock. With the LVDS electrical standard long distances and quiet operation at high rates are possible. The TI interface device accepts the seralized LVDS signals and outputs a parallel word with reference clock. The parallel word can be up to 21 bits. Each group of 7 bits are deserialized independently using the common reference clock and down converted to the parallel word. The base model "8R" uses 14 of the 21 bits for the data and control. The "2R" model uses all 21 bits of the parallel interface.

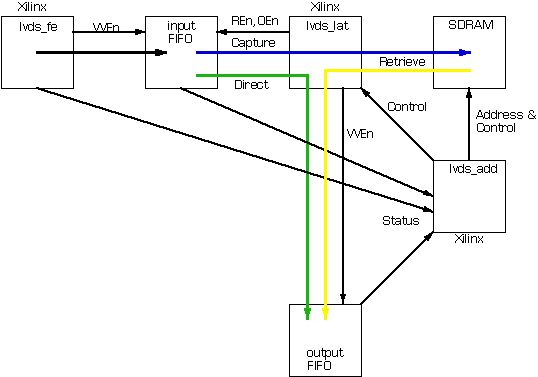

The 8 channels are programmable with the ability to enable the channels of interest, the size of the memory allocated to each channel, the method of reception and the synchronization to each transmission. Each channel is supported with independent FIFO memory at strategic locations to allow full speed operation and the use of the banked SDRAM. Tags are inserted into the bitstream which are used to determine which data to trigger on and which to store. The amount of data to capture is programmable. The amount to skip can be programmed.

Once received the data is loaded into a channel FIFO for storage until the SDRAM can read in the new data. When the FIFO has data the SDRAM controller is alerted with a request to move the data. The flags are set to use burst data movement for efficient operation. Each channel has a separate FIFO. The channels are organized into two groups of 4. Each SDRAM controller arbitrates between the 4 requesting FIFO´s to move data into the SDRAM without allowng FIFO overruns.

The Latch Xlinx converts from 32 bit FIFO to 64 bit SDRAM data and down converts the reference rate to keep the pipeline balanced. Data is moved in Bursts whenever there is enough to move a complete page. Any LW coherent size can be moved with the hardware automatically making the necessary paging adjustments.

Once loaded into the SDRAM the data is available to the system to read using DMA transfers. The amount of memory per channel is programmable: the start address for each channel can be programmed as well as the length of the data to be received allowing all of the memory to be allocated to once channel or one quarter to each channel or whatever is required. For example in the "2T" model all of the memory for each bank is allocated to a single channel in each bank. In standard "8T" operation the channels are set-up in a symmetrical fashion.

A mode is available where the "8R" operation can be performed without using the SDRAM. It is called Direct mode. One channel of the 8 can be designated to read directly from the front end receiver FIFO directly to the DMA FIFO. The data is then directly moved to system memory. This mode is useful for real time monitoring of a channel.

The first customers for the 8R and 8T needed to use multiple cards within each chassis. Specifically 10 cards were placed into an expansion chassis providing 80 channels. The power consumption is not particularly high, and with 10 cards was too much for the 5V or the 3.3V rail of the power supply. The cards come with an option to operate using the 5V or the 3.3V power rail as the main source of power to allow multple boards to be used in the same chassis without overloading the power supply - it is recommended that you mix 5V and 3.3V cards when working with multiple cards. Please note that the PCi interface is "universal voltage", and not affected by the power rail option.

For more complete information please download the hardware manuals. Bit maps, diagrams, pinouts etc. are contained within.

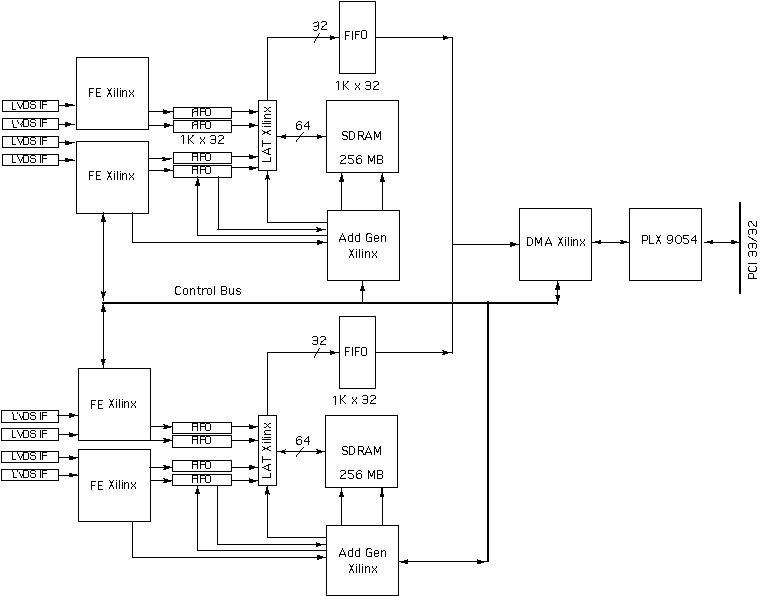

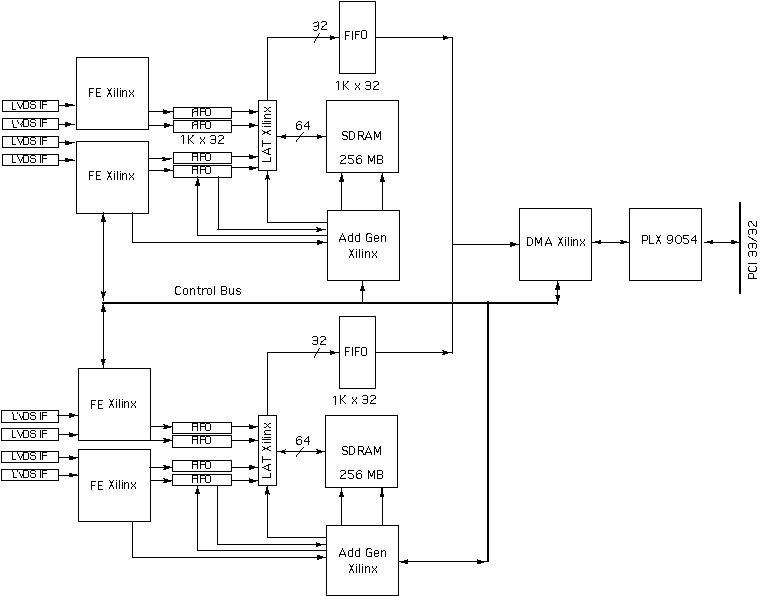

PCI-LVDS-8R block Diagram

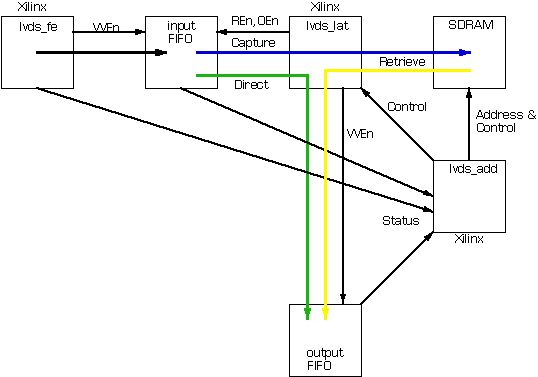

PCI-LVDS-8R Data Flow Diagram

PCI-LVDS-8R is a PCI card with 8 channels. Each channel has memory, processing, and LVDS serialized input. The input is compatible with the TIA/EIA-644 LVDS standard. The serialized data is received with parallel serial data streams plus a reference clock. With the LVDS electrical standard long distances and quiet operation at high rates are possible. The TI interface device accepts the seralized LVDS signals and outputs a parallel word with reference clock. The parallel word can be up to 21 bits. Each group of 7 bits are deserialized independently using the common reference clock and down converted to the parallel word. The base model "8R" uses 14 of the 21 bits for the data and control. The "2R" model uses all 21 bits of the parallel interface.

The 8 channels are programmable with the ability to enable the channels of interest, the size of the memory allocated to each channel, the method of reception and the synchronization to each transmission. Each channel is supported with independent FIFO memory at strategic locations to allow full speed operation and the use of the banked SDRAM. Tags are inserted into the bitstream which are used to determine which data to trigger on and which to store. The amount of data to capture is programmable. The amount to skip can be programmed.

Once received the data is loaded into a channel FIFO for storage until the SDRAM can read in the new data. When the FIFO has data the SDRAM controller is alerted with a request to move the data. The flags are set to use burst data movement for efficient operation. Each channel has a separate FIFO. The channels are organized into two groups of 4. Each SDRAM controller arbitrates between the 4 requesting FIFO´s to move data into the SDRAM without allowng FIFO overruns.

The Latch Xlinx converts from 32 bit FIFO to 64 bit SDRAM data and down converts the reference rate to keep the pipeline balanced. Data is moved in Bursts whenever there is enough to move a complete page. Any LW coherent size can be moved with the hardware automatically making the necessary paging adjustments.

Once loaded into the SDRAM the data is available to the system to read using DMA transfers. The amount of memory per channel is programmable: the start address for each channel can be programmed as well as the length of the data to be received allowing all of the memory to be allocated to once channel or one quarter to each channel or whatever is required. For example in the "2T" model all of the memory for each bank is allocated to a single channel in each bank. In standard "8T" operation the channels are set-up in a symmetrical fashion.

A mode is available where the "8R" operation can be performed without using the SDRAM. It is called Direct mode. One channel of the 8 can be designated to read directly from the front end receiver FIFO directly to the DMA FIFO. The data is then directly moved to system memory. This mode is useful for real time monitoring of a channel.

The first customers for the 8R and 8T needed to use multiple cards within each chassis. Specifically 10 cards were placed into an expansion chassis providing 80 channels. The power consumption is not particularly high, and with 10 cards was too much for the 5V or the 3.3V rail of the power supply. The cards come with an option to operate using the 5V or the 3.3V power rail as the main source of power to allow multple boards to be used in the same chassis without overloading the power supply - it is recommended that you mix 5V and 3.3V cards when working with multiple cards. Please note that the PCi interface is "universal voltage", and not affected by the power rail option.

For more complete information please download the hardware manuals. Bit maps, diagrams, pinouts etc. are contained within.

PCI-LVDS-8R block Diagram

PCI-LVDS-8R Data Flow Diagram

PCI-LVDS-8R Features

Size

Full length PCI card.

Ports

Up to 8 ports. Memory split into groups of 4. 2R version has one port per memory.

Interface

TIA/EIA-644 is the electrical standard with clock and three data streams per port.

Access Width

Standard PCI byte lanes supported for byte, word, and long-access dependent.

Access Frequency

33 MHz operation.

Software Interface

Industry Standard 31154 Bridge register definitions. The bridge does not require any user set-up. PMC register definitions as defined by installed hardware.

Interrupts

INTA routed to PCI connector. Various programmable causes to support data flow.

Power

3.V and +5V utilized

Thermal

Current design is commercial temperature. Any updated design will be industrial temperature range.

IO Interface

Main IO at the bezel. 3-M Connector. EOL will be updated in any modernization.

Specification

PCI specification compliant

DIP Switch

8 position switch is provided to allow for configuration control

PCI-LVDS-8R Benefits

Speed

PCI-LVDS-8R offers PCI DMA speed for moving data from local storage to the host system. Real time and direct mode and store and send for bursted operation. 20-85 MHz parallel rate [21 bit] data at IO [3 x 7 bit data plus clock] for 1.785 GBits / sec. Differential LVDS with 100 ohm termination for data integrity.

Price

PCI-LVDS-8R will require redesign to manufacture. Once accomplished the enhanced design will likely be PCIe based, with more memory and fewer FPGAs required for an overall cost reduction and feature expansion. Contact Dynamic Engineering for a proposal. Please include quantities and schedule. Since design is to be updated, feel free to ask for additional features to support your project.

Ease of Use

The original design and any updated design will be easy to use with reference software for the initial set-up and capture of data with PCI-LVDS-8R. Direct memory map with independent DMA ports for each channel in the new design.

Availability

Dynamic Engineering maintains a database going back to 1988. We can port a lot of the original design to the new version and fuse with enhanced features from other projects and specific to this one. The lead time will be 3 months [approximately] for the new version [initial order] - after that this product will be built to order in our manufacturing center for a much shorter lead time of a few weeks.

Size

PCI-LVDS-8R is currently a full-size PCI board, which conforms to the PCI mechanical and electrical specifications. The new version may be shorter - perhaps half length and we may put the IO on a mezzanine to allow a single base design to support both the 8R and 8T or mixed configurations.

Part Number: PCI-LVDS-8R

Ordering Options

- PCI-LVDS-8R Standard board Add any of the following build options after the PN as shown below:

- -3.3V 3.3V Power Rail Operation

- -5V 5V Power Rail Operation

- -ROHS Use ROHS processing. Standard processing is "leaded"

- -CC Option to add Conformal Coating

Breakout Kits - PCI-LVDS-8R-ENG Break Out Kit includes: Board level Schematics [PDF], LVDS Cable and Windows® XP/2000 software driver

PCI-LVDS-8T Drivers

Software Support for PCI-LVDS-8T is included in the Engineering Kit.

PCI-LVDS-8R Manuals

Click on the link to Download selected manuals in PDF format.

Download the PCI_LVDS_8R Manual updated 4/16/01 in PDF format.

Download the PCI_LVDS_2R Manual updated 12/05/07 in PDF format.

Download the PCI_LVDS_8R NT Driver Manual updated 5/6/02 in PDF format.

Download the PCI_LVDS_8R /8T Windows XP/2000 Driver Manual updated 4/20/04 in PDF format.

Download the PCI_LVDS_2R /2T Windows XP/2000 Driver Manual 07/14/06 in PDF format.

Download the PCI_LVDS_8R Manual updated 4/16/01 in PDF format.

Download the PCI_LVDS_2R Manual updated 12/05/07 in PDF format.

Download the PCI_LVDS_8R NT Driver Manual updated 5/6/02 in PDF format.

Download the PCI_LVDS_8R /8T Windows XP/2000 Driver Manual updated 4/20/04 in PDF format.

Download the PCI_LVDS_2R /2T Windows XP/2000 Driver Manual 07/14/06 in PDF format.