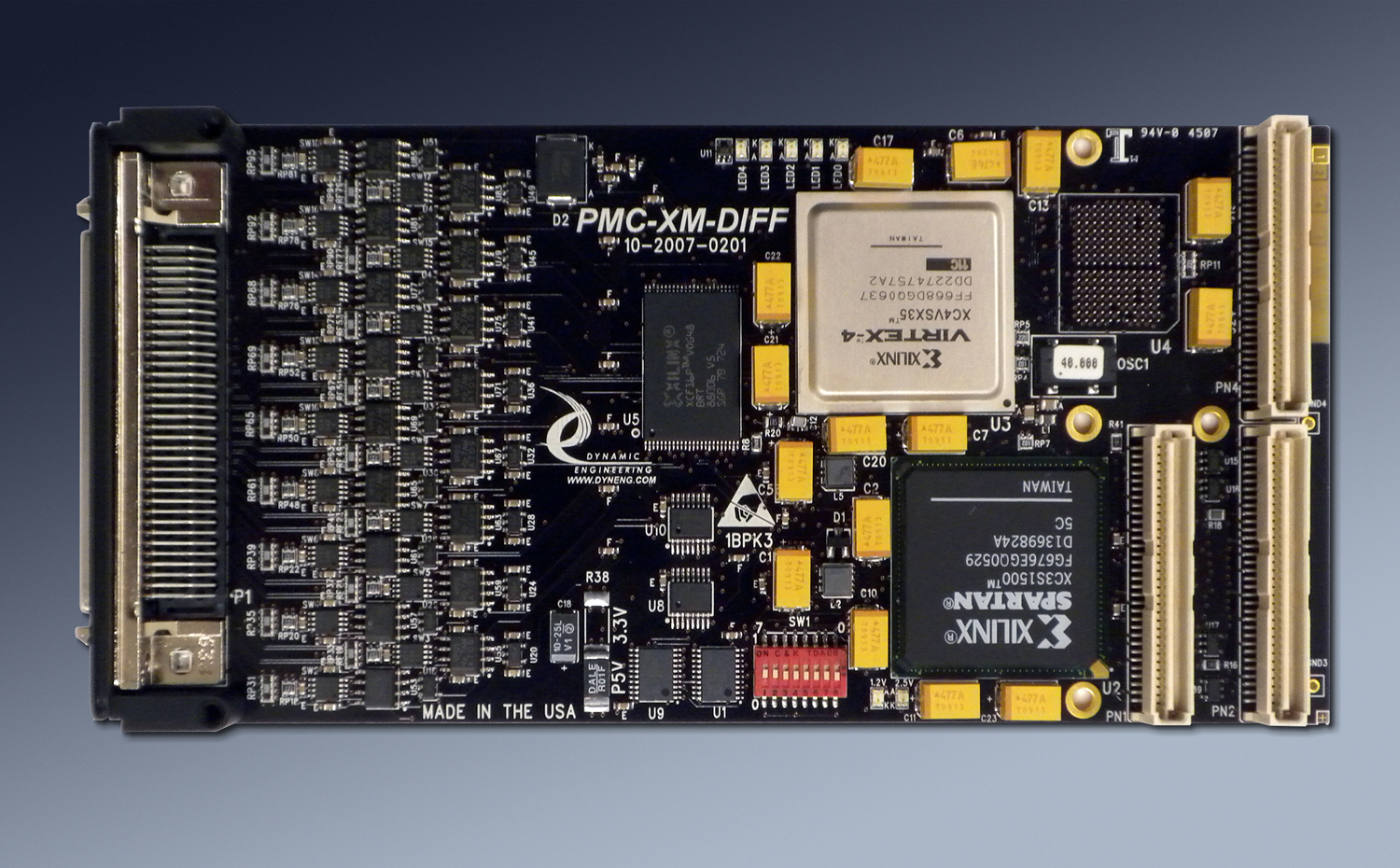

PMC-XM-DIFF

PMC Module with user programmable Spartan VI 100 FPGA

Order This Item

Contact to order this item.PMC-XM-DIFF Description

- User Programmable Spartan VI 100 FPGA

- User FPGA supported with software reload and FLASH

- Universal voltage 32 / 33 PCI interface with DMA support, 8 ports defined

- User programmable PLL

- DDR 128M x 16

- 34 LVDS and/or RS-485 IO types

- Independent Programmable Termination and Direction.

- Temperature Sensor

- Bezel IO and/or Rear IO

- Industrial Temperature standard

- 1 year warranty standard. Extended warranty available.

- ROHS and Standard processing available

Do you need to develop your own Xilinx implementation and prefer to use a COTS solution for the board? PMC-XM-DIFF is part of a family of user defined, reprogrammable FPGA based designs from Dynamic Engineering. PMC-XM-DIFF is designed to support clients who need to control the FPGA and their application uses differential IO. The IO is defined with transceivers using an SO8 package with multiple common footprint devices allowing for RS-485 and LVDS. Each IO has a separate Direction line and a dedicated analog switch to allow for termination control.

Each IO are resistor isolated from the front and rear connectors to allow front or rear operation without creating bus stubs. Each of the differential pairs is properly matched and impedance controlled. All of the IO to the front or rear panels are also matched against each other for "no skew" other than that introduced by the system cabling and active devices. 34 differential pairs are available at the front panel and/or 32 at Pn4.

The transceivers are interconnected with the FPGA to allow user control over the IO. The user FPGA is supported on many levels to make the user design implementation as easy as possible. FLASH is supplied along with a JTAG programming method to implement auto loading applications or for a default initialization of the FPGA. The FPGA can also be loaded [or over-written] using software.

The base design includes the PMC/PCI interface with DMA. The Spartan VI FPGA implements the board level decoding to allow control over the loading of the User FPGA, DMA into and out of the board, memory to support DMA, and an arbitration unit to allow multiple DMA ports to be implemented. The User FPGA device is further supported by DDR [128Mx16], PLL, Digital Temperature Sensor.

The AMD Xilinx Spartan VI FPGA has the right combination of speed, space, memory, and features to implement many embedded projects. A summary of the XC6S capabilities:

8 DCM [Digital Clock Manager] used for clock control, synthesis, phase shifting.

4 PMCD : Phase Matched Clock Divider

Clock Buffers: multiple external and internal sources can be routed with low skew buffers

160 blocks of Block RAM : each 18 Kbits

64 Extreme DSP slices: each with 18x18 multiplier, adder, and accumlator

Additional 416 Kbits of distributed RAM

59,904 Logic Cells

To make integration easy an engineering kit is available. The engineering kit has a base "footprint", written in VHDL. A windows® driver is also part of the engineering kit. Frequently clients ask Dynamic Engineering to do the initial programming for their project and then deliver a custom engineering kit with the initial implementation, custom driver and manuals to them. In this state the client can do the maintenance or add features while taking advantage of Dynamic Engineering´s expertise and familiarity with PMC-XM-DIFF.

The VHDL defined design can have any type of interface that the user wants. In the BiSerial version of the design Dynamic Engineering has implemented Manchester, Miller, Telemetry, specialized command/control, UART, SDLC and other protocols. Any of the BiSerial designs can be ported to the PMC-XM-DIFF as part of a custom implementation for your requirements. Alternatively you can implement or port existing design work to the PMC-XM-DIFF. The channelized architecture isolates the IO control from the bus control making it easy to port design work in or out.

DMA can be used to move data from the system memory to local storage within the FPGA and vice-versa. The PCI bus is 32/33 universal voltage. The interconnection between the PCI FPGA and the user FPGA is also 32 bits and operates at 33 MHz. Two channels of TX and two channels of RX DMA are supported plus standard PCI target accesses. An arbiter within the PCI FPGA takes care of monitoring the local bus between the two FPGAs. The channels have status bits used to communicate that the channel is ready to be read or loaded for DMA. There are 8 address bits for 256 x32 of register memory decoded from the PCI space. In addition there are 10 "spare" lines which could be used for address expansion or other custom purposes.

Please note PMC-XM-DIFF can be used with a PMC carrier to adapt to PCI-104, PCI, PCIe, cPCI, VME and other situations. For your convenience; Dynamic Engineering has many PMC carriers.

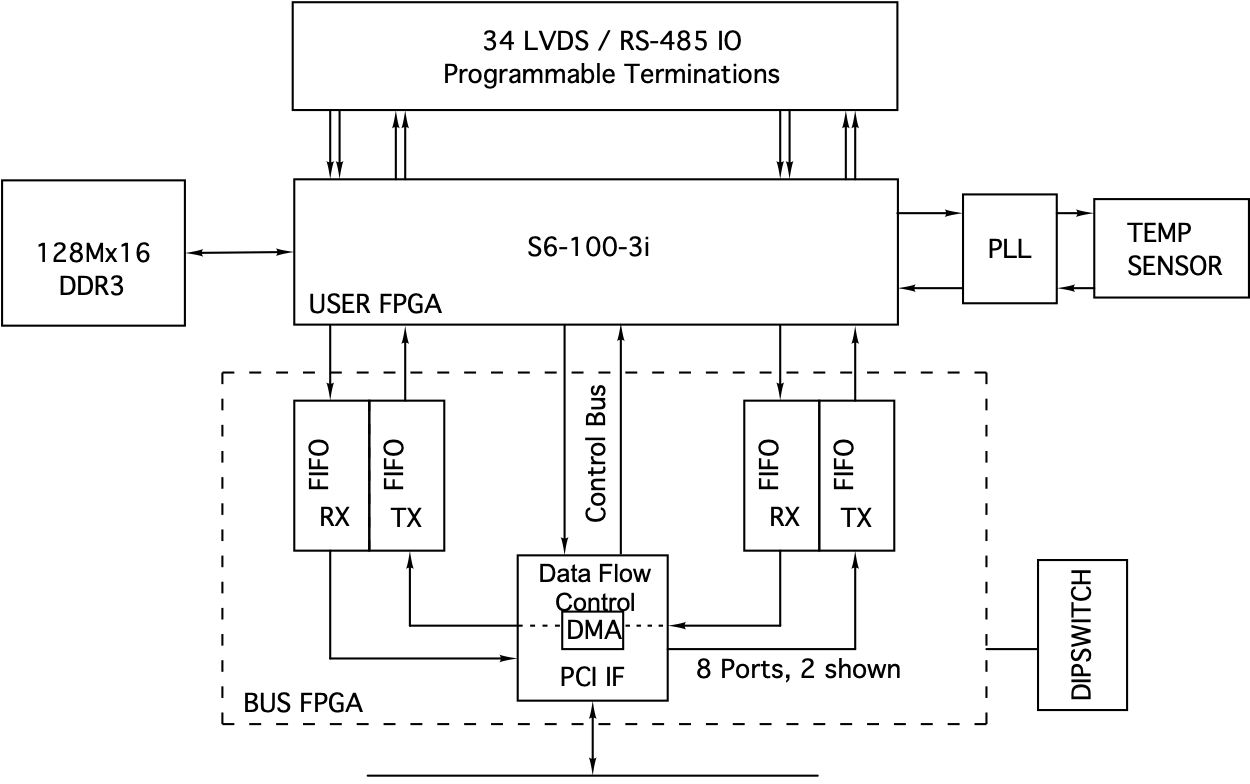

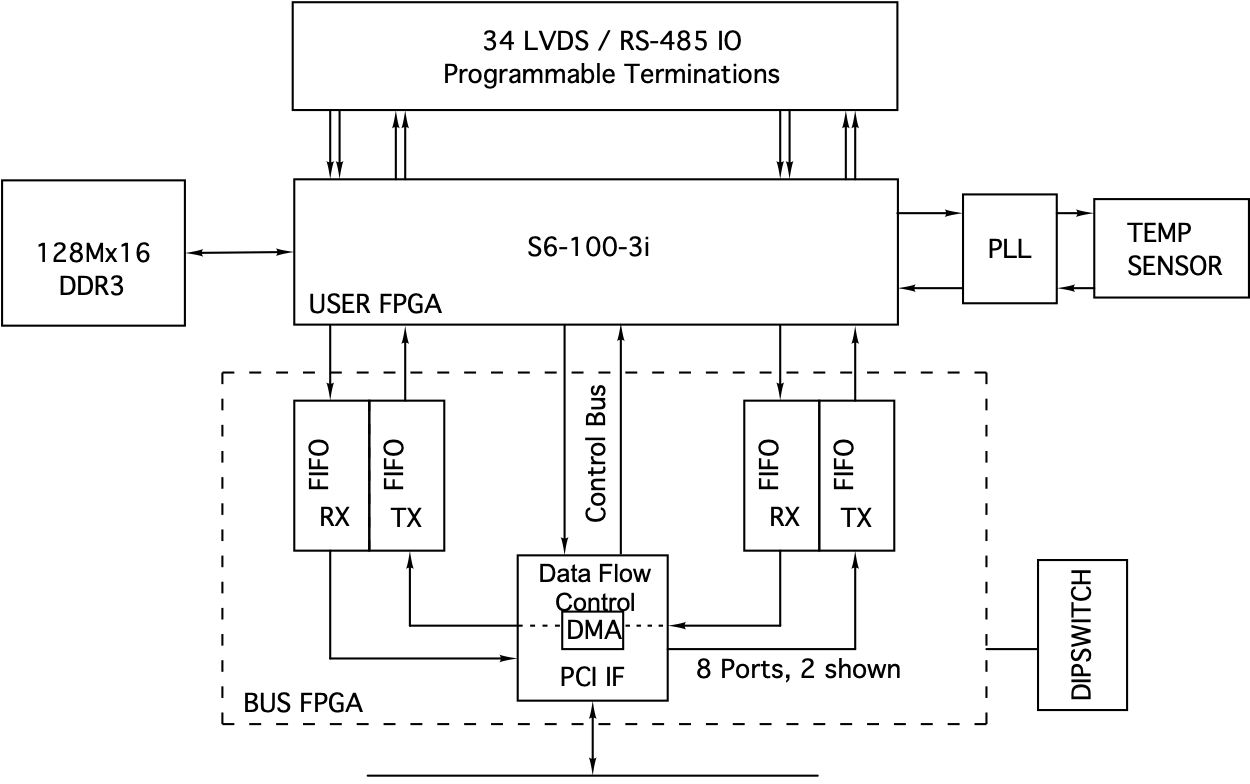

PMC-XM-DIFF Block Diagram

Each IO are resistor isolated from the front and rear connectors to allow front or rear operation without creating bus stubs. Each of the differential pairs is properly matched and impedance controlled. All of the IO to the front or rear panels are also matched against each other for "no skew" other than that introduced by the system cabling and active devices. 34 differential pairs are available at the front panel and/or 32 at Pn4.

The transceivers are interconnected with the FPGA to allow user control over the IO. The user FPGA is supported on many levels to make the user design implementation as easy as possible. FLASH is supplied along with a JTAG programming method to implement auto loading applications or for a default initialization of the FPGA. The FPGA can also be loaded [or over-written] using software.

The base design includes the PMC/PCI interface with DMA. The Spartan VI FPGA implements the board level decoding to allow control over the loading of the User FPGA, DMA into and out of the board, memory to support DMA, and an arbitration unit to allow multiple DMA ports to be implemented. The User FPGA device is further supported by DDR [128Mx16], PLL, Digital Temperature Sensor.

The AMD Xilinx Spartan VI FPGA has the right combination of speed, space, memory, and features to implement many embedded projects. A summary of the XC6S capabilities:

8 DCM [Digital Clock Manager] used for clock control, synthesis, phase shifting.

4 PMCD : Phase Matched Clock Divider

Clock Buffers: multiple external and internal sources can be routed with low skew buffers

160 blocks of Block RAM : each 18 Kbits

64 Extreme DSP slices: each with 18x18 multiplier, adder, and accumlator

Additional 416 Kbits of distributed RAM

59,904 Logic Cells

To make integration easy an engineering kit is available. The engineering kit has a base "footprint", written in VHDL. A windows® driver is also part of the engineering kit. Frequently clients ask Dynamic Engineering to do the initial programming for their project and then deliver a custom engineering kit with the initial implementation, custom driver and manuals to them. In this state the client can do the maintenance or add features while taking advantage of Dynamic Engineering´s expertise and familiarity with PMC-XM-DIFF.

The VHDL defined design can have any type of interface that the user wants. In the BiSerial version of the design Dynamic Engineering has implemented Manchester, Miller, Telemetry, specialized command/control, UART, SDLC and other protocols. Any of the BiSerial designs can be ported to the PMC-XM-DIFF as part of a custom implementation for your requirements. Alternatively you can implement or port existing design work to the PMC-XM-DIFF. The channelized architecture isolates the IO control from the bus control making it easy to port design work in or out.

DMA can be used to move data from the system memory to local storage within the FPGA and vice-versa. The PCI bus is 32/33 universal voltage. The interconnection between the PCI FPGA and the user FPGA is also 32 bits and operates at 33 MHz. Two channels of TX and two channels of RX DMA are supported plus standard PCI target accesses. An arbiter within the PCI FPGA takes care of monitoring the local bus between the two FPGAs. The channels have status bits used to communicate that the channel is ready to be read or loaded for DMA. There are 8 address bits for 256 x32 of register memory decoded from the PCI space. In addition there are 10 "spare" lines which could be used for address expansion or other custom purposes.

Please note PMC-XM-DIFF can be used with a PMC carrier to adapt to PCI-104, PCI, PCIe, cPCI, VME and other situations. For your convenience; Dynamic Engineering has many PMC carriers.

IP-429 Features

Size

1.8 x 3.9 inches nominal Type II with low profile components on rear

IO

2 independent ports based on SJA1000 and SAJ1041 combination

Clocks/Configuration

Compatible with 8 and 32 MHz IP bus operation. The CAN Controller is completely programmable to provide a variety of speeds [up to 1 MHz], IO types, and modes of operation

IP Decoding

Word, or multiple word payload [x32, x64 etc See PCIe carriers]. ID, IO, INT, MEM spaces supported.

Isolation

Optional Galvanic Isolation with isolated power supply

Software Interface

Control registers are read-writeable

Windows®, reference SW and Drivers

Windows®, reference SW and Drivers

Interrupts

Programmable interrupts for each port are supported. Masked interrupts can be used in polled mode by reading the status register. Interrupts are mapped to INTR0n on IP bus.

Power Requirement

+5V 86 mA typical in direct coupled mode

Volatility

Statement of Volatility

Reliability

TBD million hours. Bellcore. GB 25c

IP-CAN Benefits

Speed

The IP interface supports 32 MHz operation for quick data loading and unloading. The interface supports interrupts and polling. The CAN interface supports the standard rates and can be reprogrammed to alternate user requirements. Dynamic Engineering carriers support 32 to 16 conversion in HW allowing for 32 bit accesses on the host bus. Our new PCIe carriers support x8, x16, x32, and x64 accesses to the IP. Fill or read the buffers with quad accesses for higher performance.

Price

System level cost is best when reasonably priced reliable hardware is used and NRE minimized. With IP-CAN, driver support for the carrier and IP level, reference software, history of reliable operation, and fantastic client support your cost per unit and overall costs are attractive.

Ease of Use

IP-CAN is easy to use. All registers are read-write and word aligned. There is a lot of flexability with interrupt and polled mode operations. The industry standard SJA1000 CAN controller is used to provide a consistent software interface with any previous design work. Please download the manuals and see for yourself. Reference software is provided in source form to get you started. The reference software does multiple tests including loop-back.

Availability

There are 2 basic models with 2 ports of either direct or isolated CAN interface. Stocked in small quantities. Special versions and larger orders may have a delay based on part availability. An advantage of working with Dynamic Engineering is the availability of our own manufacturing capability. Production of larger orders will be faster than you might expect.

IP Specification Compatibility

IP-429 is compliant per the VITA 4 - 1995 specification. Tested with PCI and PCIe based carriers. All Dynamic Engineering IP Modules are compatible with the PCIe3IP, PCIe5IP, VPX2IP, PCI3IP, PCI5IP, cPCI2IP, cPCI4IP, PC104pIP etc. IP-429 will operate with any IP specification compliant carrier board.

Part Number: IP-429

Ordering Options

-

-40 to 85C Standard Temperature range

- IP-CAN................2 CAN Ports with Direct Coupled operation

- IP-CAN-ISO.........2 CAN ports with Isolation

- -CC Option to add Conformal Coating

IP-CAN Drivers

Software Support for IP-CAN includes: Windows® 7

The IP driver is layered and operates on top of the Carrier driver. IP drivers are auto installed for each instance detected. Please see the Driver manuals for the specifics of each type.

The Windows driver works with IP-CAN to provide direct programming in the Pelican or Standard CAN modes. The driver supports switching between modes, controlling both channels on each card, and direct mapping of the cards to the slots for positive cable assignments. The driver has been used for extensive testing with both ISO and Direct connect cards. 6 channels were interconnected with both short [several inch long] and long length cables [approximately 120 ft total length with nodes equally spaced] at the full 1 MHz bandwidth. Multiple carriers were used to support the IP´s. Linux can be used as well using the generic mode of the Linux carrier driver. A module driver is in the works.

The driver uses the carrier ID Switch to distinguish between carriers installed in the same system. The slot location determined with the initial PCI/PCIe enumeration operation is added to the switch information to create a physical location description for the card.

The IP-CAN hardware and driver can be used with any of the Dynamic Engineering IP Carriers. Porting between different form factors is low cost, and easy with software that stays consistent.

Drivers and Reference SW are developed for each type / version of IP-CAN implemented. Windows® is included with your purchase of the HW. A small one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

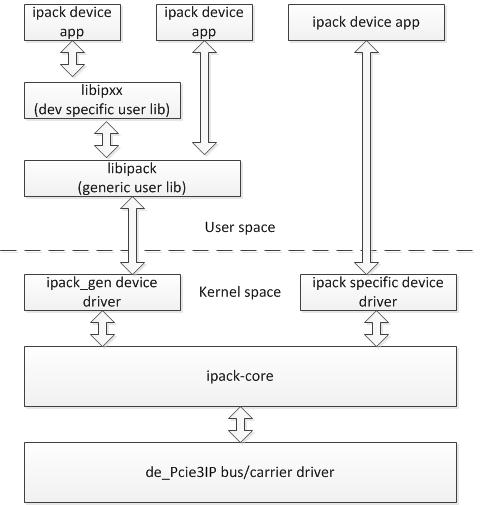

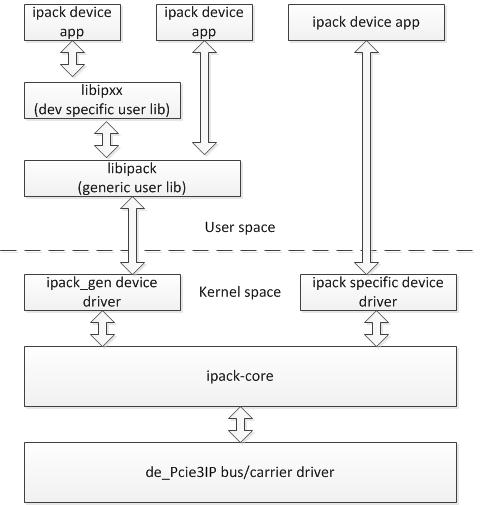

Reference diagam of how our Linux Driver / Application layer operate with the Carrier and IP Module.

The IP driver is layered and operates on top of the Carrier driver. IP drivers are auto installed for each instance detected. Please see the Driver manuals for the specifics of each type.

The Windows driver works with IP-CAN to provide direct programming in the Pelican or Standard CAN modes. The driver supports switching between modes, controlling both channels on each card, and direct mapping of the cards to the slots for positive cable assignments. The driver has been used for extensive testing with both ISO and Direct connect cards. 6 channels were interconnected with both short [several inch long] and long length cables [approximately 120 ft total length with nodes equally spaced] at the full 1 MHz bandwidth. Multiple carriers were used to support the IP´s. Linux can be used as well using the generic mode of the Linux carrier driver. A module driver is in the works.

The driver uses the carrier ID Switch to distinguish between carriers installed in the same system. The slot location determined with the initial PCI/PCIe enumeration operation is added to the switch information to create a physical location description for the card.

The IP-CAN hardware and driver can be used with any of the Dynamic Engineering IP Carriers. Porting between different form factors is low cost, and easy with software that stays consistent.

Drivers and Reference SW are developed for each type / version of IP-CAN implemented. Windows® is included with your purchase of the HW. A small one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Reference diagam of how our Linux Driver / Application layer operate with the Carrier and IP Module.

IP-CAN manuals

Click on the links to Download selected manuals in PDF format.

Download the IP Carrier and Module Quick Start guide for Windows®7

IP Carrier and Module Quick Start guide for Windows®10

IP-CAN Hardware Manual

Win7 driver installation and use manual

IP Carrier Linux Manual

Linux IP Module Manual

VxWorks IP Module Manual

Download the IP Carrier and Module Quick Start guide for Windows®7

IP Carrier and Module Quick Start guide for Windows®10

IP-CAN Hardware Manual

Win7 driver installation and use manual

IP Carrier Linux Manual

Linux IP Module Manual

VxWorks IP Module Manual