ccPMC-Parallel-TTL

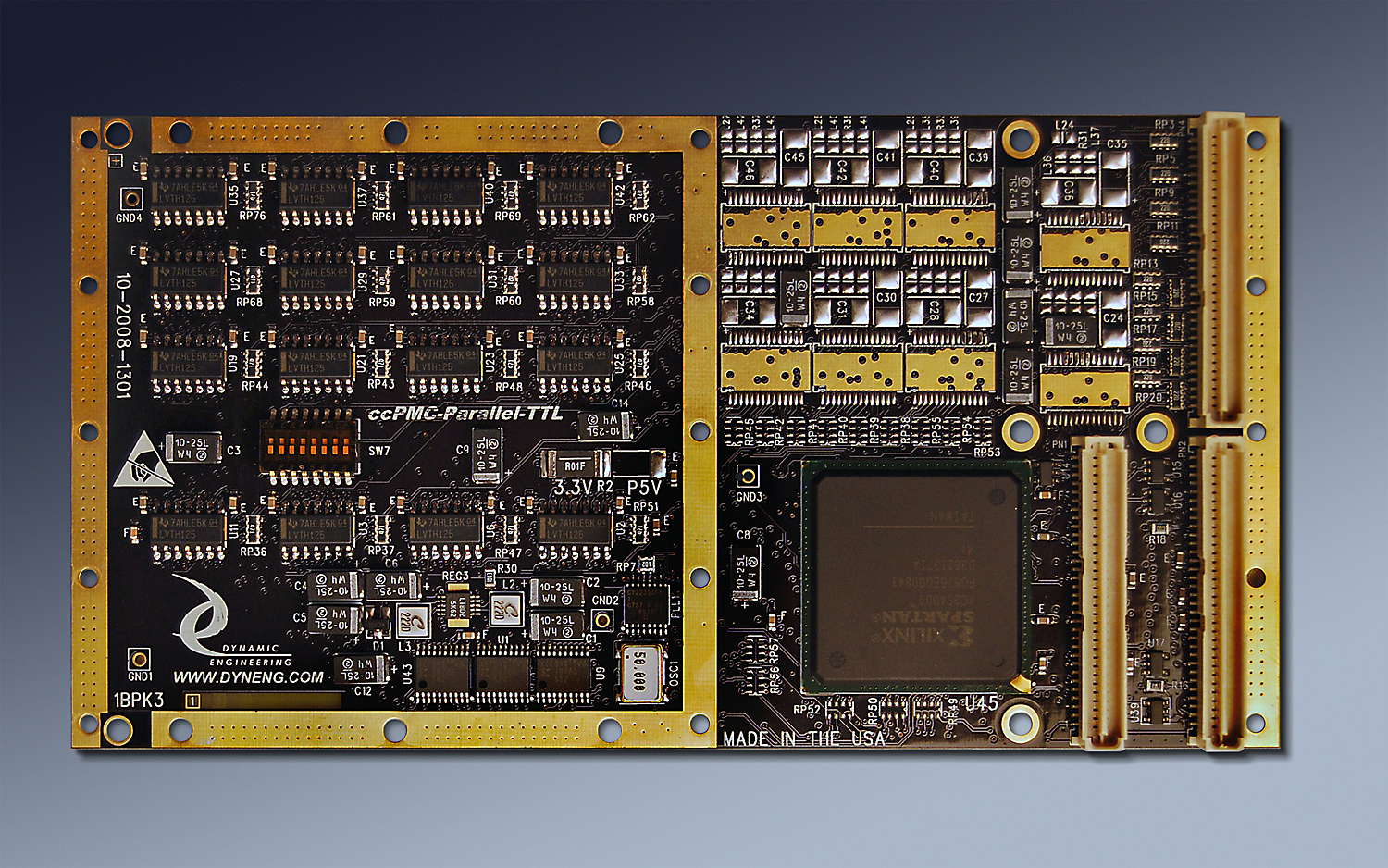

Conduction Cooled PMC Module with Spartan III FPGA, PLL, up to 64 Independent Single Ended IO, up to 8 ADC

Order This Item

ccPMC-Parallel-TTL Description

- Windows, Linux,

- Standard PMC module

- 32/33 with DMA operation

- 64 TTL and 8 ADC options for IO

- Rear IO

- Spartan 3 FPGA with BRAM for FIFO or RAM implementation

- PLL with 4 clock references

- 1 year warranty standard. Extended warranty available.

- Extended [Industrial] Temperature standard. -40C ⇔ +85C

- ROHS and Standard processing available

Does your system require single ended TTL or CMOS level signals? How about medium speed Analog data capture [ADC 1-10 MHz]? Dynamic Engineering has a multitude of solutions covering different architectures and mezzanine types. With most architectures you have a choice with carriers for cPCI, PCI, PCIe, VME, VPX, PCI-104, and other buses for XMC, PMC and IP mezzanine modules. Usually your choice is based on other system constraints as various modules can provide the IO you require. Dynamic Engineering can assist in your decision making regarding architecture and other trade-offs. Dynamic Engineering has carriers for most architectures, and is adding more as new solutions are requested by our clients.

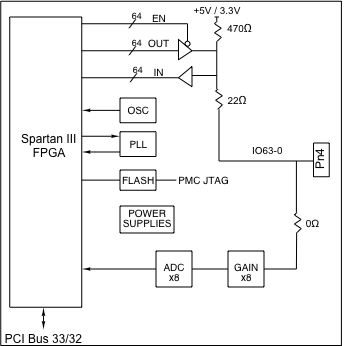

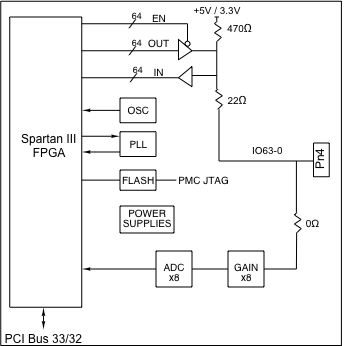

The Conduction Cooled PMC compatible ccPMC-Parallel-TTL has build options to have up to 64 independent digital IO and up to 8 ADC channels. The high density makes efficient use of precious PMC slot resources. The IO is available for system connection through the rear [Pn4] connector. The rear panel IO has a PIM and PIM Carrier available for rear panel wiring options. The HDEterm68 can be used as a breakout for the rear panel IO when the PMC carrier has a SCSI style connector for the rear IO. The HDEcabl68 provides a convenient cable. The pin definitions are consistent with the PMC Parallel IO and PMC Parallel TTL designs to enable users to migrate to the ccPMC-Parallel-TTL quickly and easily when a conduction cooled solution is required.

Each TTL IO is independently programmable. The outputs can be enabled and driven high or low. When disabled on-board pull-ups terminate the lines. The pull-ups can be referenced to 5V or 3.3V as an ordering option. A master enable is available to allow the user to synchronize the upper and lower outputs for coherant 64 bit operation in a 32 bit system. The master enable can be set to allow independent upper and lower bank updates.

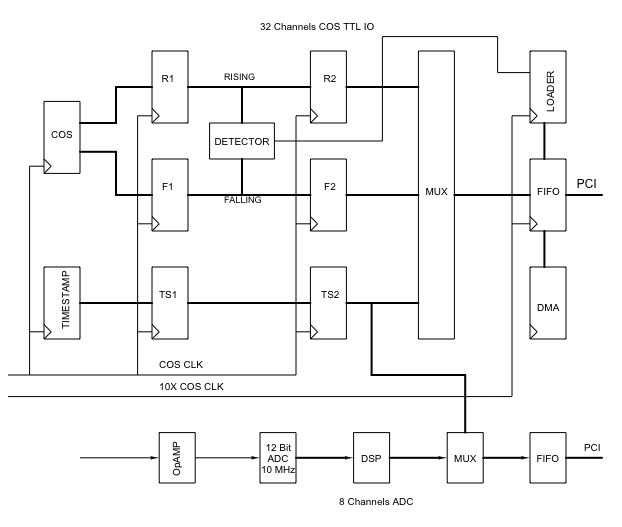

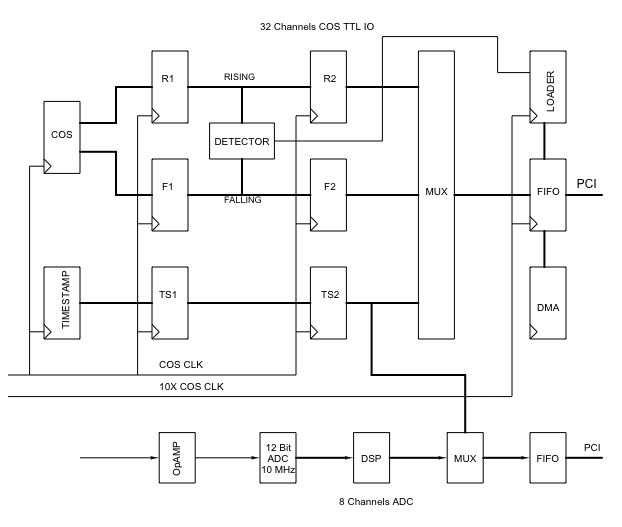

All TTL channels can be read as inputs regardless of the transmit enable programming. Local loop-back can be used for BIT. All IO channels can be used as interrupt generators. Interrupts are programmable to be based on either or both edges for "Change of State" operation. An external clock, PCI clock, or oscillator can be selected for the reference on the COS operation. The reference can be programmed to be divided to create lower frequencies. A PLL is available to support user frequency selection to provide the right sampling rate for your application.

All of the IO are routed through the FPGA device to allow for custom applications that require hardware intervention or specific timing. For example the design of the ccPMC Parallel TTL supports internal FIFOs and DMA. With an added state-machine for your interface the hardware can provide much more than a simple parallel interface. Contact Dynamic Engineering for convenient customer specific implementations.

ccPMC-Parallel-TTL has an option to remove some of the TTL and replace them with ADC. The lower 32 bits can be removed and 8 - 12 bit ADCs installed instead. Each ADC can be programmed to operate at frequencies up to 10 MHz. Options for synchronous sampling across channels and independent reference frequencies under software control. The ADCs can be programmed for different voltage ranges with a pair of resistors. The ADC is a 0-5V model. WIth matching resistors 0-10V is scaled etc. Each ADC has a high bandwidth opamp buffer to support high frequencies with low current requirements [in the input signal]. Please contact Dynamic Engineering with your requirements.

Each of the ADC channels can be supported with memory, DMA, data/signal processing, etc. For example; The BA18 version of ccPMC Parallel TTL has 32 TTL lines, and 8 ADCs. Each ADC has a separate DMA channel and FIFO memory support. The data is sampled and tested against the current reference sample. When the new sample exceeds the range established by the current sample it is saved into the FIFO along with the Time Tag and used as an updated reference sample. The range is programmable [ sample - lower offset <=> sample + upper offset]. With the Time Tag a known number of in range samples occurred between the data stored. Data reduction at the source reduces CPU processing later and bus overhead. Tell us what features you require.

The base model has a simple to use register based interface. The registers are mapped as 32 bit words. All registers are read-writeable. The Windows® compatible [XP/2000] driver is available to provide the system level interface for this design. Use standard C/C++ to control your hardware or use the Hardware manual to make your own software interface. The manuals for the different implementations are available for download from the bottom of this page.

All parts are industrial temp or better [-40C <=> +85C]. Conformal coating, thermal gluing and thermal foam are available options help adapt to your environment.

The Conduction Cooled PMC compatible ccPMC-Parallel-TTL has build options to have up to 64 independent digital IO and up to 8 ADC channels. The high density makes efficient use of precious PMC slot resources. The IO is available for system connection through the rear [Pn4] connector. The rear panel IO has a PIM and PIM Carrier available for rear panel wiring options. The HDEterm68 can be used as a breakout for the rear panel IO when the PMC carrier has a SCSI style connector for the rear IO. The HDEcabl68 provides a convenient cable. The pin definitions are consistent with the PMC Parallel IO and PMC Parallel TTL designs to enable users to migrate to the ccPMC-Parallel-TTL quickly and easily when a conduction cooled solution is required.

Each TTL IO is independently programmable. The outputs can be enabled and driven high or low. When disabled on-board pull-ups terminate the lines. The pull-ups can be referenced to 5V or 3.3V as an ordering option. A master enable is available to allow the user to synchronize the upper and lower outputs for coherant 64 bit operation in a 32 bit system. The master enable can be set to allow independent upper and lower bank updates.

All TTL channels can be read as inputs regardless of the transmit enable programming. Local loop-back can be used for BIT. All IO channels can be used as interrupt generators. Interrupts are programmable to be based on either or both edges for "Change of State" operation. An external clock, PCI clock, or oscillator can be selected for the reference on the COS operation. The reference can be programmed to be divided to create lower frequencies. A PLL is available to support user frequency selection to provide the right sampling rate for your application.

All of the IO are routed through the FPGA device to allow for custom applications that require hardware intervention or specific timing. For example the design of the ccPMC Parallel TTL supports internal FIFOs and DMA. With an added state-machine for your interface the hardware can provide much more than a simple parallel interface. Contact Dynamic Engineering for convenient customer specific implementations.

ccPMC-Parallel-TTL has an option to remove some of the TTL and replace them with ADC. The lower 32 bits can be removed and 8 - 12 bit ADCs installed instead. Each ADC can be programmed to operate at frequencies up to 10 MHz. Options for synchronous sampling across channels and independent reference frequencies under software control. The ADCs can be programmed for different voltage ranges with a pair of resistors. The ADC is a 0-5V model. WIth matching resistors 0-10V is scaled etc. Each ADC has a high bandwidth opamp buffer to support high frequencies with low current requirements [in the input signal]. Please contact Dynamic Engineering with your requirements.

Each of the ADC channels can be supported with memory, DMA, data/signal processing, etc. For example; The BA18 version of ccPMC Parallel TTL has 32 TTL lines, and 8 ADCs. Each ADC has a separate DMA channel and FIFO memory support. The data is sampled and tested against the current reference sample. When the new sample exceeds the range established by the current sample it is saved into the FIFO along with the Time Tag and used as an updated reference sample. The range is programmable [ sample - lower offset <=> sample + upper offset]. With the Time Tag a known number of in range samples occurred between the data stored. Data reduction at the source reduces CPU processing later and bus overhead. Tell us what features you require.

The base model has a simple to use register based interface. The registers are mapped as 32 bit words. All registers are read-writeable. The Windows® compatible [XP/2000] driver is available to provide the system level interface for this design. Use standard C/C++ to control your hardware or use the Hardware manual to make your own software interface. The manuals for the different implementations are available for download from the bottom of this page.

All parts are industrial temp or better [-40C <=> +85C]. Conformal coating, thermal gluing and thermal foam are available options help adapt to your environment.

ccPMC-Parallel-TTLFeatures

Size

Std ccPMC 74mm x 143.75mm nominal. Low profile components on rear

Parallel Interface

64 independent TTL IO. The pull-ups can be referenced to 3.3V or 5V. Rear IO [Pn4] Unused ports isolated with resistors for "zero bus stub". Matched IO within 1/1000 inch for on-board traces.

Analog Interface

8 independent / synchronized ADC. 12 bit 10 MHz capable ADCs with opamp buffers and voltage dividers. FIFO support with DMA for each channel. Signal Processing on received data or straight packed data.

Clocks

33 MHz PCI, 50 MHz oscillator ( other frequencies available), 4 programmable PLL inputs, Counters/Dividers/DCM for local clock control.

Interface Types

Custom programmed interfaces are available. Please send us a timing diagram, and we can program one for you. Most interfaces can be adapted from our large library including the updated VHDL, Windows or Linux Driver, reference manuals etc. We can support on-site [ours] integration to help you get your application level software working.

Alternatively choose one of the already completed versions and purchase off-the-shelf. Common requested and implemented interface types include: Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. Mix and Match.

Alternatively choose one of the already completed versions and purchase off-the-shelf. Common requested and implemented interface types include: Manchester, Miller, SDLC, UART, Serial, Parallel, GPIO, COS, Custom, LADEE, NMS, Camera, Ternary, Low Speed, High Speed, Telemetry, Master & Target interactive IO, Adaptive. Mix and Match.

Memory

Spartan 3 - 1000, 2000, 4000 sizes, BRAMs to create RAM, FIFO etc.

Software Interface

Control registers are read-writeable

Windows®, and Linux reference SW and Drivers

Windows®, and Linux reference SW and Drivers

Interrupts

Software programmable interrupts on status, errors, completion of transfer, DMA, FIFO levels, custom events. Status can be polled for non-interrupt driven operation as well.

Power Requirement

3.3V and +5V. The 5V is converted to 2.5, 1.2 local DC:DC power supplies for efficient power conversion. 3.3 and 5V rails should be applied together.

Volatility

Reliability

TBD million hours. Bellcore. GB 25c

ccPMC-Parallel-TTL Benefits

Speed

ccPMC-Parallel-TTL is a software controlled HW interface. As fast as the PCI interface can push the data across, the outputs can change. With the Windows® driver several accesses per microsecond can be achieved. Your time to market will be shortened by the easy to use interface, flexibility in design, and off-the-shelf availability. With DMA enabled and FIFOs instantiated faster transfers can occur. Up to 48K x 32 internal FIFO can be achieved with the 4000 sized FPGA.

Price

ccPMC-Parallel-TTL has an attractive price, and low integration cost for a low system cost. ccPMC-Parallel-TTL has an associated PIM and PIM Carrier which can lead to further savings in cPCI environments.

Ease of Use

ccPMC-Parallel-TTL is designed to be easy to use. Direct access to all features, aligned registers for larger access types, programmable features to allow personalization for your system. Please download the manuals and see for yourself. Reference software is provided in source form to get you started.

Availability

This model is built to order. With our on-site manufacturing the production delays are minimized.

PMC Specification Compatibility

ccPMC-Parallel-TTL is compliant per the VITA PMC/CMC specifications. Tested with PCI and PCIe based carriers. All Dynamic Engineering PMC Modules are compatible with the PCIeBPMCX1, ccPMC-Parallel-TTL will operate with any PMC specification compliant carrier board.

Part Number: ccPMC-Parallel-XXX

Ordering Options

- ccPMC-Parallel-XXX Standard board - with Industrial temperature components. Replace XXX with specific model ordered

- -TTL TTL IO only model

- -ADC 8 ADC with no TTL

- -ROHS Use ROHS processing. Standard processing is "leaded"

- -CC Option to add Conformal Coating

- -XXX See Models section for customized versions and replace XXX with type "BA17" for example

ccPMC-Parallel-TTL Drivers

Software Support for ccPMC-Parallel-XXX includes: Windows®, and Linux compliant drivers. VxWorks by special request.

Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type/version of ccPMC-Parallel-TTL implemented. When custom versions are ordered the NRE will include providing Windows, Linux, and/or VxWorks packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. A one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

Please see the Driver manuals for the specifics of each type.

Drivers and Reference SW are developed for each type/version of ccPMC-Parallel-TTL implemented. When custom versions are ordered the NRE will include providing Windows, Linux, and/or VxWorks packages. For off-the-shelf models, select on the manuals tab, the Windows® and Linux SW shown is included with your purchase of the HW. A one-time charge is required for the VxWorks versions. Unsupported SW versions may have an NRE requirement.

Integration support is available. Please contact Dynamic Engineering for this option or download the Technical Support Description from the Company button.

ccPMC-Parallel-TTL Models

Customer: Boeing

COS with Time Stamp and 16Kx32 storage plus 8 channels of ADC 10 MHz 12 bit with

independent DMA and storage. Unfiltered or Data compression on ADC channels with

programmable thresholds. Programmable clock rates for COS, Time Stamp and ADCs

Download the ccPMC-Parallel-TTL-BA18 Rev A1 Hardware Manual in Adobe Acrobat PDF format.

Download the ccPMC-Parallel-TTL-BA18 Rev A Windows® Driver Manual in Adobe Acrobat PDF format.

Client: Boeing

COS with Time Stamp and 16Kx32 storage plus 8 channels of ADC 10 MHz 12 bit with

independent DMA and storage. Unfiltered or Data compression on ADC channels with

programmable thresholds. Programmable clock rates for COS, Time Stamp and ADCs

Download the ccPMC-Parallel-TTL-BA18 Rev A1 Hardware Manual in Adobe Acrobat PDF format.

Download the ccPMC-Parallel-TTL-BA18 Rev A Windows® Driver Manual in Adobe Acrobat PDF format.

Client: Boeing